# S32Z2/E2

# SESIP Security Target Rev. 1.2 — 17 July 2025

#### **Document information**

| Information | Content                                                                                                                                                                            |  |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Keywords    | SESIP, Security Target, S32Z2/E2, S32Z2x, S32E2x                                                                                                                                   |  |  |  |

| Abstract    | Security target for evaluation of the S32Z2/E2 developed and provided by NXP Semiconductors, according to SESIP Assurance Level 2 (SESIP2) based on SESIP methodology, version 1.2 |  |  |  |

**SESIP Security Target**

# **Revision History**

| Rev. | Date          | Description                                                  |  |

|------|---------------|--------------------------------------------------------------|--|

| 1.0  | 14 April 2025 | First Release for SESIP Evaluation                           |  |

| 1.1  | 16 April 2025 | Update 3.3.2.2 Field Return of Platform                      |  |

| 1.2  | 17 July 2025  | TOE Identification to align with Ref Manual (S32Z2x, S32E2x) |  |

# 1 Introduction

This Security Target describes the S32Z2/E2 platform and the exact security properties of the platform that are evaluated against GlobalPlatform Technology Security Evaluation Standard for IoT Platforms (SESIP), version 1.2, SESIP Assurance Level 2 (SESIP2) [2].

This Security Target also complies with the CEN norm EN 17927:2023 [1].

#### 1.1 ST Reference

S32Z2/E2, SESIP Security Target, Revision 1.2, NXP Semiconductors, 17 July 2025.

#### 1.2 SESIP Profile Reference and Conformance Claims

Table 1. SESIP Profile Reference and Conformance Claims

| Reference       | Value                                                                |  |  |

|-----------------|----------------------------------------------------------------------|--|--|

| SP Name         | GlobalPlatform Technology SESIP Profile for Secure MCUs and MPUs [3] |  |  |

| SP Version      | Version 1.0                                                          |  |  |

| Assurance Claim | SESIP Assurance Level 2 (SESIP2)                                     |  |  |

| Package Claim   | Base SP, Package Security Services, Package Software Isolation       |  |  |

#### 1.3 Platform Reference

#### S32Z2/E2

Table 2. Platform Reference

| Reference                 | Value                                   |

|---------------------------|-----------------------------------------|

| Platform Name and Version | S32Z2/E2, Rev 1.0                       |

|                           | HSE Firmware for S32Z2, x.2.58.0, x=0/1 |

| Platform Identification   | S32Z2x, S32E2x                          |

| Platform Type             | Automotive Real-Time Processor          |

#### 1.4 Included Guidance Documents

The following documents are included with the platform:

**Table 3. Guidance Documents**

| Document                                                                          | Reference                                                                        |  |  |

|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|--|

| SESIP Security Target                                                             | S32Z2/E2, SESIP Security Target, Revision 1.2, NXP Semiconductors, 17 July 2025. |  |  |

| Reference Manual                                                                  | S32Z2 Reference Manual [6]                                                       |  |  |

| Security Application Note                                                         | S32ZE Security Overview [5]                                                      |  |  |

| Firmware Reference Manual                                                         | HSE_H/M Firmware Reference Manual [9]                                            |  |  |

| Firmware API Reference Manual                                                     | HSE Service API Reference Manual for S32ZE [7]                                   |  |  |

| Product Data Sheet                                                                | S32Z2 Data Sheet [4]                                                             |  |  |

| Application Note AN649711, Selecting and using cryptographic algorithms and proto |                                                                                  |  |  |

S32Z2/E2

#### 1.5 Other Certification

S32Z2/E2 development process has followed Business Creation and Management (BCaM) framework and is subject to Product Security Incident Response Process (PSIRP). The latest NXP (BCaM and PSIRP) processes have been certified as compliant following ISO/SAE 21434:2021 Road vehicles - cybersecurity engineering [14]. See more in Section 3.2.1.

| Item                                         | Content                      |  |  |

|----------------------------------------------|------------------------------|--|--|

| Scheme                                       | ISO/SAE 21434:2021 [14]      |  |  |

| Certification body                           | TÜV SÜD Product Service GmbH |  |  |

| Certification number Q4B 109577 0002 Rev. 00 |                              |  |  |

| Certification date                           | 2021-09-06                   |  |  |

The RNG IP implemented in S32Z2/E2 has also been CAVP validated according to NISP SP 800-90A Hash-DRBG with SHA256 [13].

| Item                 | Content                                                                                               |  |  |

|----------------------|-------------------------------------------------------------------------------------------------------|--|--|

| Scheme               | Cryptographic Algorithm Validation Program (CAVP)                                                     |  |  |

| Certification body   | National Institute of Standards and Technology (NIST)                                                 |  |  |

| Certification number | A5258 https://csrc.nist.gov/projects/cryptographic-algorithm-validation-program/details?product=17907 |  |  |

| Certification date   | 22 April 2024                                                                                         |  |  |

#### 1.6 Platform Overview and Description

The Platform S32Z2/E2 high-performance real-time processors combine real-time and DSP/ML processing with hardware virtualization, scalable non-volatile memory, flexible expansion memory support and network acceleration including an EVITA Full SHE+ ISO/SAE 21434 compliant hardware security engine. The S32Z2/E2 help enable software-defined vehicles, reduce software integration complexity and enhance safety and security, developed in accordance with the ISO 26262 SEoOC methodology, and supporting ASIL D functional safety.

The S32Z2/E2 family includes:

- 2 Real-Time core Clusters (RTU)

- · DSP/ML processor

- · Memory Subsystem

- System Management Unit (SMU)

- · System Control and Safety Unit

- Ethernet acceleration

- Auto Communication Acceleration with a Flexible Low-Latency Communication Engine (FlexLLCE) to enable safe and secure CAN gateway acceleration

- Hardware Security Engine (HSE)

- · Multiple Communication Interfaces

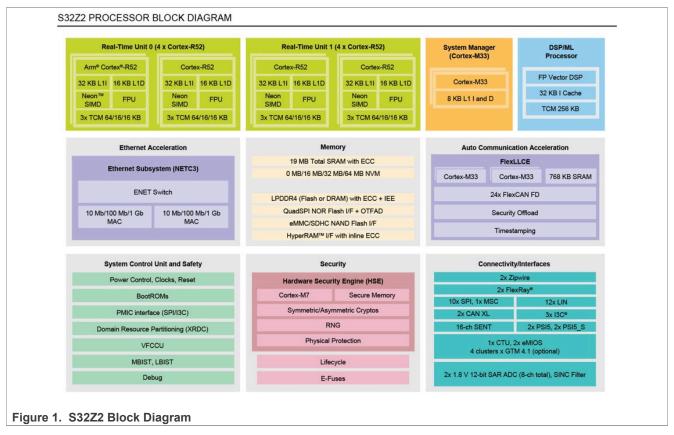

Figure 1 shows the block diagram of the S32Z Core.

**SESIP Security Target**

S32E2 processors target electric vehicle (xEV) control and smart actuation applications and are exactly software compatible with S32Z2 processors, but are packaged with additional Complex Timers and Actuation controllers.

The platform will be used by the application developer for final automotive use cases.

#### 1.6.1 Real-Time Unit SubSystem

The S32Z2/E2 has 2 identically configured instances of RTU Syubsystem (RTU0 and RTU1). Each RTU Subsystem includes:

- 4 ARM<sup>®</sup> Cortex<sup>®</sup>-R52 processors, each of which integrates ARM<sup>®</sup> Neon<sup>™</sup> SIMD technology and can be clocked at up to 1GHz.

- 32KB of 4-way set associative instruction cache and 16 KB of 4-way set associative data cache.

- 1MB of 8-way set associative Last-Level Cache (LLC).

- · A Smart Prefetch Unit between LLC and External Memory Interface

- · Low latency peripheral bridge that connects to a set of Messaging units

#### 1.6.2 Memory

Each RTU subsystem has access to several memories that are optimized both for real-time application performance and to support large program spaces. The memory is arranged hierarchically and the performance of each memory depends on its location in the hierarchy. Memory close to the cores has a lower access time than the memory that is placed further away. To achieve optimal performance, an application must use each of these memories for the most appropriate function.

#### 1.6.3 DSP / ML

CEVA Sens-Pro Floating Point 2 (SPF2), which brings a performance enhancement for larger vector / matrix calculations.

#### 1.6.4 FlexLLCE

The Flexible Low Latency Communications Engine subsystem supports CAN communications. It offloads AUTOSAR CAN functions from the RTU core clusters. FlexLLCE includes:

- 2 ARM® Cortex®x-M33 core pairs operating in lockstep clocked at 400 MHz

- 768 KB of local FlexLLCE SRAM

- 24 independent CAN modules that support CAN 2.0 and CAN FD standards

- CAN hub that allows multiple CAN modules to share a single CAN bus (up to 3 on-chip CAN bus networks)

- · Hardware Lookup table (LUT) for CAN message routing

- · AES accelerator for CAN message authentication

- Dedicated multichannel DMA for transfer of CAN messages

# 1.6.5 Hardware Security Engine (HSE)

The Hardware Security Engine, which is the "H" variant of the (HSE) subsystem, also referred as HSE in the rest of this document. It has its own exclusive system resources and connects to the host via a dedicated interface.

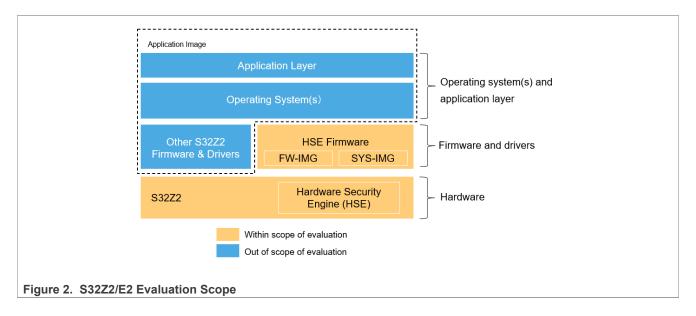

Specifically for flash loadable image, in the security domain, the flash loadable HSE firmware includes:

- The HSE firmware executable, hereafter referred to as FW-IMG. For instance, crypto library is included in FW-IMG.

- The HSE system image that contains public and private (secret) keys and configuration data (i.e. HSE system attributes, CR/SMR entries, OTFAD contexts), hereafter referred to as SYS-IMG

NXP offers standard and premium versions for HSE firmware, which are all in evaluation scope, while the premium version provides expanded security capabilities. See <u>Table 4</u> for the difference between the standard version and the premium version.

Any additional firmware, OS or application software is stored in the application domain on the platform, is not in scope of this evaluation, and is referred as application image hereafter.

Table 4. HSE Firmware Difference: Standard vs Premium

| HSE firmware variant                                    | Standard      | Premium           |

|---------------------------------------------------------|---------------|-------------------|

| ECC max key size                                        | 256 bits      | 640 bits          |

| RSA max key size                                        | 2048 bits     | 4096 bits         |

| HMAC max key size                                       | 512 bits      | 1152 bits         |

| Number of keys in RAM                                   | 20            | User configurable |

| Number of symmetric keys in NVM                         | 40            | User configurable |

| Number of asymmetric keys in NVM                        | 12            | User configurable |

| SHA3, IPSec, Classic DH, and Burmester-Desmedt services | Not supported | Supported         |

| CURVE25519 (Montgomery and Twisted)                     | Supported     | Supported         |

| CURVE448 (Montgomery and Twisted)                       | Not Supported | Supported         |

**SESIP Security Target**

#### 1.6.6 Platform Security Features

The Hardware Security Engine (HSE\_H) is a subsystem that implements the security functions for the device. It provides cryptographic services to the host CPUs and the network accelerators, and fully meets the functional goals and objectives of the common automotive security specifications Secure Hardware Extension (SHE+), Hardware Security Module (HSM), and E-safety Vehicle Intrusion Protected Application (EVITA) Full.

The HSE\_H subsystem is responsible for establishing the root of trust on the device during the boot process and includes the following features:

- · Secure boot of customer code using asymmetric or symmetric keys

- · Highly featured symmetric and asymmetric accelerators

- Support for various cryptographic functions (see Section 3.3.4.1)

- Arm® Cortex®-M7 CPU

- True Random Number Generator (TRNG)

- Pseudo Random Number Generator (PRNG)

- · Firmware Over-the-Air (FOTA) support.

- · Secure Debug

#### 1.6.7 Platform Physical Scope

The physical scope is the S32Z die including the on-chip ROM, the components of which die are given in Figure 1 and described in Section 2.2 of [4]. External memory interface details are given Table 4, section 53.2.7.2 and section 65.6.5 [6] as well as in Section 14.4 of [4].

#### 1.6.8 Platform Logical Scope

The Target Of Evaluation (TOE) is the hardware (including the on-chip ROM) and the flash loadable updatable HSE firmware (i.e. FW-IMG and SYS-IMG) (either standard version or premium version) as shown in <u>Figure 2</u>. The versions for each components are as listed in <u>Table 5</u>. Note that SYS-IMG contains keys and configurable data which is not a static image hence not listed in the table.

Any additional firmware, OS or application software stored on the platform (i.e. application image) is not in scope of this evaluation.

Table 5. Platform Deliverables

| Туре         | Name                   | Release                                                   | Form of delivery             |

|--------------|------------------------|-----------------------------------------------------------|------------------------------|

| IC Hardware  | S32Z2/E2               | Rev 1.0                                                   | Silicon Chip and On Chip ROM |

| HSE Firmware | HSE Firmware for S32Z2 | x.2.58.0<br>x=0, Standard Version<br>x=1, Premium Version | Software package             |

**SESIP Security Target**

#### 1.6.9 Required Non-Platform Hardware/Software/Firmware

See Table 4 of [6] for compatible external flash.

S32Z2/E2 also supports external DRAM (See [6]) but the functions in the evaluation scope only use internal SRAM hence the DRAM is not required.

#### 1.6.10 LifeCycle

The lifecycle (LC) is managed by the HSE subsystem, see Section 3.3.8 of [9] for further information.

The LC states after NXP manufacturing are as <u>Table 6</u>:

Table 6. Life Cycle States

| LC State    | Description                                                                                                                                      |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Production  | Device (i.e. NXP's IC) is under development at NXP                                                                                               |  |  |

| CUST_DEL    | Device (i.e. NXP's IC) delivered to system integrator (i.e. NXP's customer) for ECU manufacturing and initial configuration                      |  |  |

| OEM_PROD    | ECU (device) delivered to the OEM for vehicle integration and final configuration                                                                |  |  |

| IN_FIELD    | ECU integrated in the vehicle and operating; this is the state of normal device use (and most secure state)                                      |  |  |

| PRE_FA mode | Normal device usage. Additionally, it provides capabilities for failure analysis. This mode is available within OEM_PROD and IN_FIELD lifecycle. |  |  |

| FA          | ECU (device) failure; this is the state for functional testing of the IC                                                                         |  |  |

NXP ensures secure provisioning of the NXP credentials and secure life cycle configuration. NXP's customer (also referred as OEM) will receive the device in CUST\_DEL state, and shall perform software installation and configuration and OEM credential provision in CUST\_DEL and OEM\_PROD states and then configure the device to IN\_FIELD state in their technical and/or procedural secure environment. The IN\_FIELD state is the normal device use state. The PRE\_FA and FA states can be reached from the OEM\_PROD and IN\_FIELD states, and switching into FA needs both OEM and NXP credential authentication.

**SESIP Security Target**

# 1.6.11 Configurations

#### **Base SP Security Functional Requirements**

The MCU/MPU ensures the execution of platform trusted code, and in particular the functions related to, secure boot, updatability and code isolation.

#### **Security services**

The base security features are complemented by security services intended to be used by the higher software layers to implement a full-fledged Root-of-Trust and operating system.

#### **Software Isolation**

The base security features are complemented by mechanisms needed to cover the use case where the final IoT product allows the execution of untrusted code and/or requires access restrictions to the platform features by the upper level.

#### 1.6.12 Use Case

#### [trusted user only]

The final product is expected to be installed and operated inside a vehicle within a secured enclosure, hence it is not expected to be physically accessible to unknown or untrusted users.

#### [any code]

The final product is expected to run only authorized code, but it cannot be excluded that the product executes code which is unknown to the product developer or which is unintentionally harmfull to the platform.

# 2 Security Objectives for the Operational Environment

# 2.1 Platform Objectives for the Operational Environment

For the platform to fulfill its security requirements, the operational environment (technical or procedural) <u>must</u> fulfill the following objectives:

Table 7. Platform Objectives for the Operational Environment

| Title                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Reference                                   |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| Platform<br>Verification                         | The operating system or application code are expected to verify the correct version of all platform components it depends on, and it shall match the corresponding information from the guidance document.                                                                                                                                                                                                                                                                              | Section 3.3.1.1                             |

| Secure Boot                                      | The operating system or application code are expected to make use of the Secure Boot Mode by blowing the BOOT_CFGn, FUSE_SEL, FUSE_CFG_LOCK and IVT_AUTH fuses, by setting the IVT Boot Configuration Word [BOOT_SEC], by configuring the Memory Verification Services, and by securely provisionning device-dependent ADPK.                                                                                                                                                            | Section 61 and 121 of [6] Section 8 of [9], |

| Secure Debug                                     | In order to meet the physical attacker resistance, the integrating environment is expected to configure the debug functionality as described in Section 3.6.2 of [9] by securely provisioning a device-dependent ADPK.                                                                                                                                                                                                                                                                  | Section 3.6.2 of [9].                       |

| Protection<br>from Attacker's<br>Physical Access | The operational environment must protect the TOE against physical access of attackers. Note: The TOE protects itself against LIMITED physical attacker resistance.                                                                                                                                                                                                                                                                                                                      | Section 1.6.12                              |

| Ensure UID<br>Uniqueness                         | The platform has a 64-bit UID and NXP ensures uniqueness across platform instances. Although the probability is low to have the same UID for a platform instance with another type of device, the actors in charge of platform management shall ensure there is no UID confliction, and hence the UID is unique to the platform instance depending on use case.                                                                                                                         | Section 2.1                                 |

| Key<br>Management out<br>of the Platform         | Cryptographic keys and certificates outside of the Platform are subject to secure key management procedures. Keys shall be provisioned for corresponding security functions, including: attestation, memory authentication and encryption, secure debug.                                                                                                                                                                                                                                | Section 7 of [9]                            |

| Secure Update                                    | The operating system or application code are expected to enable secure communication for security update, and in case of update, the update image is expected to be properly signed and distributed in secure manner as well. The operating system or application code are expected to use the anti-roll back feature. As a flash-less device, there is finite number of anti-roll back counter updates (fuses) and further procedure shall be taken once the counter limit is reached. | Sections 6.5 and 11 of [9]                  |

| SW Integration                                   | The operating system or application code are expected to ensure the correct version of the HSE firmware is integrated and configured                                                                                                                                                                                                                                                                                                                                                    | Sections 4 and 5 of [9]                     |

| Memory<br>Protection                             | For IP and data that needs protection in authenticity, integrity and confidentiality, memory verification function (SMR Authentication, SMR Decryption) and Flash encryption (OTFAD) shall be used.                                                                                                                                                                                                                                                                                     | Section 8 and 10.2 of [9]                   |

| Lifecycle<br>Management                          | The operating system or application code are expected to configure the LC state according the stage of product development and deployment.                                                                                                                                                                                                                                                                                                                                              | Section 3.3.8 of [9]                        |

| Cryptographic<br>Algorithm and<br>Key Length     | A few well-established cryptographic algorithms supported by the platform is of known limitation, e.g. SHA1, and key length for each algorithm has a direct impact on the cryptographic strength. The operating system or application code are expected to select an appropriate algorithm and key length set to fulfill the security requirement for the intended use case.                                                                                                            | [8]                                         |

**SESIP Security Target**

# 3 Security Requirements and Implementation

# 3.1 Security Assurance Requirements

The claimed assurance requirements package is: **SESIP Assurance Level 2 (SESIP2)** as defined in Chapter 4 of GlobalPlatform Technology Security Evaluation Standard for IoT Platforms (SESIP), version 1.2 [2].

## 3.1.1 Flaw Reporting Procedures (ALC\_FLR.2)

In accordance with the requirement for flaw reporting procedures (ALC\_FLR.2), the developer has defined the following procedure:

NXP has defined a Product Security Incident Response Process (PSIRP), implemented by a dedicated team (PSIRT). This process provides a publicly available interface (<a href="https://nxp.com/psirt">https://nxp.com/psirt</a>), and includes four major steps:

- **Reporting**. The process begins when the PSIRT becomes aware of a potential security vulnerability in an NXP product. The reporter receives an acknowledgment and updates throughout the handling process.

- **Evaluation**. The PSIRT confirms the potential vulnerability, assesses the risk, determines the impact and assigns a processing priority. If the vulnerability is confirmed, the priority determines how the issue is handled throughout the remaining steps in the process.

- Solution. Working with PSIRT, the product team develops a solution that mitigates the reported security

vulnerability. Solutions will take different forms based on the vulnerability. Because of the nature of NXP

products mostly silicon products where the firmware is in ROM -, very often the solution can only be

provided in a next version of the chips and the short-term solution will consist of recommending security

measures to be applied in systems using the NXP product.

- **Communication**. As said above, because of the nature of the NXP products, the solution to systems using the affected products often needs to be found in additional countermeasures in those systems. The communication on the vulnerability and solutions will in most cases be done directly towards the affected customers. For previously unknown or unreported issues, NXP will acknowledge the reporter of the issues (unless the reporter requests otherwise).

The hardware and firmware located in the on-chip ROM of S32Z2/E2 cannot be updated due to their immutable nature. The HSE Firmware has the capability of change and the platform's Secure Boot feature is able to verify the authenticity of HSE Firmware during the initial boot and outside of the boot sequence. See <u>Section 3.3.2.1</u> for further information.

The platform's Secure Boot feature further supports to verify the authenticity of customer code, providing an appropriate mechanism for supporting the update of customer code. The update mechanism beyond has to be provided by the customer, and such mechanism as well as the customer code is not in scope of this evaluation.

# 3.2 Security Process Packages

#### 3.2.1 Secure Development

For the development of the platform, the secure development process specified in ISO/SAE 21434:2021 Road vehicles - cybersecurity engineering [14] has been applied to the platform.

#### Conformance rationale:

This product was designed for maximum compliance with ISO/SAE 21434:2021 Road vehicles - cybersecurity engineering [14].

During the development, the project ensured that the existing work products could be mapped onto the work products expected by the DIS/FDIS of ISO/SAE 21434 standard.

S32Z2/E2

**SESIP Security Target**

The NXP-wide BCaM framework is a product development process framework that covers all harmonized processes to successfully launch new products, including new technologies and/or software. It was built on best practices and now serves as NXP's platform for continuous improvements. This process framework applies to all of NXP's R&D projects and enables NXP to work together more efficiently and effectively worldwide.

The BCaM framework includes a Security Module, with the Security Maturity Process (SMP) at its centre. This process is designed to ensure that product security is given due consideration throughout the development cycle beginning with incorporating security in the product architecture – in a concept of 'Security-by-Design' - and then approving Security Milestones during development. Security Milestones align with the BCaM product development project gates and milestones with the aim to ensure that security related deliverables and reviews are planned accordingly, and eventually successfully completed for each Security Milestone, and hence for each product development gate/milestone.

NXP's BCaM process and its Product Security Incident Response Process (PSIRP), introduced in <u>Section 3.1.1</u>, are certified as compliant with the new standard ISO/SAE 21434:2021 Road vehicles - cybersecurity engineering [14]. See <a href="https://www.nxp.com/docs/en/company-information/TUV-SUV-ISO21434-CERTIFICATE.pdf">https://www.nxp.com/docs/en/company-information/TUV-SUV-ISO21434-CERTIFICATE.pdf</a>.

## 3.3 Security Functional Requirements

In the following Security Functional Requirements, the term **platform** covers the **S32Z2/E2 physical and logical scope**, and the term **application** refer to any additional firmware, OS or application software which is out of evaluation scope. It represents a part of the final connected device.

S32Z2/E2 fulfils the following security functional requirements:

## 3.3.1 Identification and Attestation of Platforms and Applications

#### 3.3.1.1 Verification of Platform Identity

The platform provides a unique identification of the platform, including all its parts and their versions.

#### Conformance rationale:

The hardware identification and version can be obtained by reading register SIUL2 MCU ID Register #1 (MIDR1) per Section 52.6.2 of [6].

The Platform Identification can be obtained using JTAG as per Section 134.5.3 of [6].

HSE Firmware version is readable by using HSE Get Attribute Services and hseAttrFwVersion\_t. (See Section 9.1.3 of [9]).

The production validation process ensures that the SFR behaves correctly.

#### 3.3.1.2 Verification of Platform Instance Identity

The platform provides a unique identification of that specific instantiation of the platform, including all its parts.

#### Conformance rationale:

A 64-bit unique device identifier (UID) is provisioned. See Section 3.2.3 of [9]. It can be retrieved via JTAG (see sections 134.13.2.20 and 134.13.2.21 of [6]) or via the service defined by the structure hseSheGetIdSrv\_t (see section 9.6 of [9]).

The production validation process ensures that the SFR behaves correctly.

#### 3.3.1.3 Attestation of Platform Genuineness

The platform provides an attestation of the "Verification of Platform Identity" and "Verification of Platform Instance Identity", in a way that cannot be cloned or changed without detection.

#### Conformance rationale:

HSE Firmware provides SHE-UID retrieve function via the service defined by the structure hseSheGetIdSrv\_t. This function returns the UID and the HSE status with a CMAC value. The CMAC is calculated over the input challenge, the UID and the status, and the key used is MASTER\_ECU\_KEY. Hence both the platform instance identity and the status are attested. See Section 9.6 of [9].

The production validation process ensures that the SFR behaves correctly.

#### 3.3.1.4 Attestation of Platform State

The platform provides an attestation of the state of the platform, such that it can be determined that the platform is in a known state.

#### Conformance rationale:

See Section 3.3.1.3, 8 bit of HSE status is returned with CMAC protection.

#### 3.3.1.5 Secure Initialization of Platform

The platform ensures its integrity and authenticity during the platform initialization. If the platform integrity and authenticity cannot be ensured, the platform will go to *reset state*.

#### Conformance rationale:

BootROM has the responsibility to authenticate, decrypt and load HSE Firmware when performing a secure boot operation. Then HSE Firmware will take over and is capable to authenticate the system image. The authentication scheme followed by BootROM to accomplish secure boot is shown in Sections 3 and 8 of [9].

The production validation process ensures that the SFR behaves correctly.

#### 3.3.2 Product Lifecycle: Factory Reset / Install / Update / Decommission

#### 3.3.2.1 Secure Update of Platform

The platform can be updated to a newer version in the field such that the *confidentiality*, integrity and authenticity of the platform is maintained.

#### Conformance rationale:

The host can update FW-IMG via the service defined by the structure hseFirmwareUpdateSrv\_t. See Section 11 of [9].

The SYS-IMG is updatable. See Section 6.5 of [9].

Memory verification services by HSE provides capability of secure update of the application image. See Section 8 of [9].

An anti-rollback protection is provided on both FW-IMG and SYS-IMG, which prevents the possibility to use a previous version of those images when they have been replaced by newer versions. See Section 11.3 of [9].

The production validation process ensures that the SFR behaves correctly and supports the ALC\_FLR.2 procedures as referenced in <u>Section 3.1.1</u>.

#### 3.3.2.2 Field Return of Platform

The platform can be returned to the vendor without user data.

#### Conformance rationale:

The Life Cycle states are described in Section 1.6.10 and Chapter 3.3.8 of [9].

**PRE\_FA mode** is not a persistent lifecycle, but enables a limited set of test features. Entering this mode is only possible from **OEM\_PROD** or **IN\_FIELD** with both OEM credentials (ADKP) and NXP credentials to enable a limited set of test features whilst retaining the possibility to return to **OEM\_PROD** or **IN\_FIELD** lifecycle state after a reset.

**FA** is a destructive life-cycle state for functional testing of the IC. Transition to **FA** lifecycle state (from any state) requires NXP credentials and is irreversible. Once in **FA** mode, device specific keys used to encrypt FW-IMG and SYS-IMG are irreversibly destroyed, hence all stored assets and information encrypted by the keys in HSE firmware are no longer accessible.

The production validation process ensures that the SFR behaves correctly.

#### 3.3.3 Extra Attacker Resistance

#### 3.3.3.1 Limited Physical Attacker Resistance

The platform detects or prevents attacks by an attacker with physical access before the attacker compromises Verification of Platform Identity, Verification of Platform Instance Identity, Attestation of Platform Genuineness, Attestation of Platform State, ecure Initialization of Platform, Secure Update of Platform, Field Return of Platform, Software Attacker Resistance:Isolation of Platform, Cryptographic Operation, Cryptographic Key Generation, Cryptographic KeyStore, Cryptographic Random Number Generator, Secure External Storage (FW-IMG, SYS-IMG and Secure Memory Region), Residual Information Purging, Reliable Index and Secure Debugging.

#### Conformance rationale:

Countermeasures are implemented to harden the boot ROM and IPs and the functions provided by boot ROM provides resistant against physical attacks.

The cryptographic library has protections against fault injection and side channel analysis.

Software protections in ROM and loadable firmware, and hardware protections (voltage, temperature, frequency detectors) are in place against fault injections. See Section 121 of [6].

The internal vulnerability analysis process ensures that the SFR behaves correctly.

#### 3.3.3.2 Software Attacker Resistance: Isolation of Platform

The platform provides isolation between the application and itself, such that an attacker able to run code as an application on the platform cannot compromise any other claimed security functional requirements.

#### Conformance rationale:

The Hardware Security Engine (HSE) is the security subsystem, which enforces security measures for the application during system start-up and run-time, safekeeps security-sensitive information (e.g. secret key values) for the application, and offloads the application from processing cryptographic operations with dedicated coprocessors. It is isolated from the host by having its own exclusive system resources and connecting to the host via a dedicated interface (Messaging Unit - MU). See Section 3.5.1 of [9].

The production validation and internal vulnerability analysis processes ensure that the SFR behaves correctly.

# 3.3.4 Cryptographic Functionality

# 3.3.4.1 Cryptographic Operation

The platform provides operations in <u>Table 8</u> functionality with algorithms in <u>Table 8</u> as specified in <u>specifications</u> in <u>Table 8</u> for key lengths described in <u>Table 8</u> and modes described in <u>Table 8</u>.

**Table 8. Cryptographic Operations**

| Operation                                                                         | Algorithm                                        | Specification                                    | Key Lengths                                                 | Modes                                            |

|-----------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------|

| Operation                                                                         | Algorithm                                        | -                                                |                                                             |                                                  |

| Encryption and decryption                                                         | AES                                              | NIST FIPS 197<br>NIST SP 800-38A                 | 128, 192, 256                                               | ECB, CBC, CTR, CFB, OFB                          |

| Encryption and decryption                                                         | AES-XTS                                          | IEEE 1619-2018;<br>January 2019                  | 128, 256                                                    | AES-XTS                                          |

| MAC generation and verification                                                   | AES                                              | RFC 3566<br>NIST SP 800-38B<br>NIST SP 800-38D   | 128                                                         | XCBC-MAC [1], CMAC,<br>GMAC                      |

| MAC generation and verification                                                   | SHA 1, SHA 2 <sup>[2]</sup>                      | FIPS PUB 198-1                                   | Up to 512 <sup>[3]</sup> , or<br>Up to 1152 <sup>[1]</sup>  | НМАС                                             |

| MAC generation and verification                                                   | SipHash                                          | [10]                                             | 64 <sup>[2]</sup> , 128                                     | CMAC, CBC-MAC, Retail MAC                        |

| Hashing                                                                           | SHA 1 <sup>[2]</sup>                             | NIST FIPS 180-4                                  | 160                                                         | -                                                |

| Hashing                                                                           | SHA 2 <sup>[2]</sup>                             | NIST FIPS 180-4                                  | 224, 256, 384, 512                                          | -                                                |

| Hashing                                                                           | SHA 3 <sup>[1]</sup>                             | NIST FIPS 202                                    | 224, 256, 384, 512                                          | -                                                |

| Hashing                                                                           | Miyaguchi-<br>Preneel<br>Compression with<br>AES | [11]                                             | 128                                                         | -                                                |

| Network ~Protocol<br>Acceleration                                                 | CRC-32<br>CRC-32C                                | IEEE-802<br>IETF-3385                            | n/a                                                         | IEEE 802.3 (aka CRC-32<br>CRC-32C (aka CRC-32/4) |

| Authenticated encryption with associated data (AEAD) and authenticated decryption | AES                                              | NIST SP 800-38D<br>NIST SP 800-38C               | 128, 192, 256                                               | GCM, CCM                                         |

| Signature<br>generation and<br>verification                                       | RSA                                              | PKCS#1 v2.2                                      | Up to 2048 <sup>[3]</sup> , or<br>Up to 4096 <sup>[1]</sup> | PKCS1 v1.5, PSS                                  |

| Signature<br>generation and<br>verification                                       | ECDSA                                            | Standards for Efficient<br>Cryptography 1 (SEC1) | Up to 256 <sup>[3]</sup> , or<br>Up to 640 <sup>[1]</sup>   | -                                                |

| Signature<br>generation and<br>verification                                       | EdDSA [2]                                        | RFC8032                                          | 256, 448                                                    | Ed25519, Ed448                                   |

| Encryption, decryption                                                            | RSA                                              | PKCS#1 v2.2                                      | Up to 2048 <sup>[3]</sup> , or Up to 4096 <sup>[1]</sup>    | PKCS1 v1.5, OAEP padding                         |

| KDF                                                                               | CKDF                                             | NIST SP 800-108<br>NIST SP 800-56C R1            | See CMAC and HMAC or Hashing                                | -                                                |

**SESIP Security Target**

Table 8. Cryptographic Operations...continued

| Operation    | Algorithm                                                        | Specification                             | Key Lengths                                              | Modes |

|--------------|------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------|-------|

| KDF          | PBKDF2                                                           | RFC8018                                   | See HMAC                                                 | -     |

| KDF          | TLS v1.2 PRF                                                     | RFC 5246, RFC 7627,<br>RFC 4279, RFC 5489 |                                                          |       |

| KDF          | HKDF                                                             | RFC 5869                                  | See HMAC                                                 |       |

| KDF          | The internet Key<br>Exchange V2<br>(IKEv2) rekeying<br>functions | RFC 4306                                  |                                                          |       |

| KDF          | Standards<br>for Efficient<br>Cryptography 1<br>(SEC1)           | ANSI X9.63                                |                                                          |       |

| KDF          | ISO18033 KDF1,<br>KDF2                                           | ISO/IEC 18033-2:2006                      |                                                          |       |

| Key Exchange | ECDH                                                             | NIST FIPS 800-56A                         | Up to 256 <sup>[3]</sup> , or Up to 512 <sup>[1]</sup>   | -     |

| Key Exchange | Classic DH                                                       | [12]                                      | Up to 2048 <sup>[3]</sup> , or Up to 4096 <sup>[1]</sup> | -     |

<sup>[1]</sup> Only supported by HSE premium firmware.

#### Conformance rationale:

Cryptographic operations are provided by HSE and HSE Firmware. See Section 7 of [9].

The production validation process ensures that the SFR behaves correctly. Additionally, the SFR is validated by NXP ACVP lab against NIST CAVP.

# 3.3.4.2 Cryptographic Key Generation

The platform provides a way to generate cryptographic keys for use in *algorithms in <u>Table 9</u>* as specified in *specifications in <u>Table 9</u>* for key lengths *described in <u>Table 9</u>*

Table 9. Cryptographic Key Generation

| ID      | Algorithm                  | Specification | Key Lengths                                                |

|---------|----------------------------|---------------|------------------------------------------------------------|

| AES     | Random Number<br>Generator |               | 128, 192, 256                                              |

| HMAC    | Random Number<br>Generator |               | Up to 512 <sup>[1]</sup> , or<br>Up to 1152 <sup>[2]</sup> |

| SIPHASH | Random Number<br>Generator |               | 64, 128                                                    |

| ECC     | ECC                        | ANSI X9.62    | Up to 256 <sup>[1]</sup> , or Up to 640 <sup>[2]</sup>     |

| RSA     | RSA                        | PKCS#1        | Up to 2048 <sup>[1]</sup> , or Up to 4096 <sup>[2]</sup>   |

<sup>[2]</sup> Refer to [8] for considerations on algorithm and key lengths.

<sup>[3]</sup> Supported by HSE standard firmware.

**SESIP Security Target**

- [1] Supported by HSE standard firmware.

- [2] Only supported by HSE premium firmware.

#### Conformance rationale:

Cryptographic key generations are provided by HSE and HSE Firmware. See Section 7.2 of [9].

The production validation process ensures that the SFR behaves correctly. Additionally, the SFR is validated by NXP ACVP lab against NIST CAVP.

#### 3.3.4.3 Cryptographic KeyStore

The platform provides a way to store *cryptographic keys* such that not even the application can compromise the *confidentiality, integrity, authenticity* of this data. This data can be used for the cryptographic operations *encryption, decryption, signature generation, MAC generation, key derivation, shared secret generation.*

#### Conformance rationale:

HSE Firmware provides key management functions. NVM and RAM key properties and values are stored and updated within SYS-IMG and saved securely in NVM by device specific keys. Furthermore, policies and access right authentications are implemented, and key access right is determined by execution rights, Host Identity (HID), and key attributes. See Sections 7.1 to 7.3 of [9].

The production validation process ensures that the SFR behaves correctly.

#### 3.3.4.4 Cryptographic Random Number Generation

The platform provides a way based on *physical noise* to generate random numbers to as specified in *NIST.SP.800-90B*.

The platform provides a way based on *DRBG* to generate random numbers to as specified in *NIST.SP.800-90A Hash-DRBG with SHA256*.

#### **Conformance rationale:**

In the HSE, the source of entropy is provided by the physical true random number generator, and the generation function is part of a Deterministic Random Number Generator (DRNG, aka DRBG or PRNG) module as defined in NIST SP 800-90A and CAVP certified (refer to Section 1.5).

Furthermore, TRNG is capable to pass AIS 31 statistical tests T0-T8.

See more in Section 7.5 of [9].

The production validation process ensures that the SFR behaves correctly. Additionally, the SFR is validated by NXP ACVP lab against NIST CAVP.

#### 3.3.5 Compliance Functionality

#### 3.3.5.1 Secure Data Serialization (FW-IMG, SYS-IMG and Secure Memory Region)

The platform ensures that all data stored outside the direct control of the platform, except for *non-secure memory regions* is protected such that the *confidentiality, integrity, authenticity, binding to the platform instance, versioning* is ensured.

#### Conformance rationale:

Both FW-IMG and SYS-IMG are encrypted and authenticated with device-dependent keys (See Section 3.3.7 of [9]).

**SESIP Security Target**

A secure memory region (SMR) is defined by a start address and a size, associated to a proof of authenticity, either a MAC or RSA/ECC signature. The host can define up to 32 SMRs clustered into the SMR table which is stored in SYS-IMG. See Section 8 of [9].

An anti-rollback protection by fuses is provided on both FW-IMG and SYS-IMG, which prevents the possibility to use a previous version of those images when they have been replaced by newer versions. As SMR table is stored in SYS-IMG, its binding to platform instance and versioning is also achievable by SYS-IMG encryption, authentication and anti-rollback.

The production validation process ensures that the SFR behaves correctly.

#### 3.3.5.2 Secure Data Serialization (On-the-fly AES decryption)

The platform ensures that all data stored outside the direct control of the platform, except for *data not in the protected regions*, is protected such that the *confidentiality* is ensured.

#### Conformance rationale:

Application code and data stored encrypted in an external Flash accessible via the QuadSPI can be decrypted via the On-the-fly AES decryption (OTFAD), in complete transparency ("on-the-fly") for the host and with zero latency (no additional read cycles). See Section 10.2 of [9].

The production validation process ensures that the SFR behaves correctly.

## 3.3.5.3 Residual Information Purging

The platform ensures that *keys with matched host identity*, with the exception of *none*, is erased using the method specified in *FIPS 140-3 using overwriting with Zeros* before the memory is used by the platform or application again and before an attacker can access it.

#### Conformance rationale:

NVM and RAM key slots can be securely deleted by the host via a service defined by the structure hseEraseKeysSrv t. See Section 7.2.9 of [9].

The production validation process ensures that the SFR behaves correctly.

#### 3.3.5.4 Reliable Index

The platform implements a strictly increasing function.

#### Conformance rationale:

HSE FW provides Monotonic Counters Services. The HSE monotonic counters are 64-bit integers that can be read and only incremented until saturation. See more in Section 10.1 of [9].

The production validation process ensures that the SFR behaves correctly.

#### 3.3.5.5 Secure Debugging

The platform only provides JTAG interface authenticated as specified in NIST FIPS 197 & NIST SP800-38A with debug functionality.

The platform ensures that all data stored by the application, with the exception of no data, is made unavailable.

#### Conformance rationale:

The debugging of the HSE subsystem and associated firmware is restricted to NXP engineering teams.

**SESIP Security Target**

In OEM\_PROD, IN-FIELD, and PRE\_FA lifecycle state, the host debug is protected by an AES ECB challenge/ response authentication or permanently disabled by configuring the DEBUG\_DISABLE OTP. See more in Section 3.6.2 of [9] .

The production validation process ensures that the SFR behaves correctly.

# 4 Mapping and Sufficiency Rationales

# 4.1 SESIP2 Sufficiency

Table 10. SESIP2 Sufficiency

| Assurance Class                 | Assurance Family                                                | Covered By                                                                                                          | Rationale                                                                                                                                                                                                                                          |

|---------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASE: Security target evaluation | ASE_INT.1 ST Introduction                                       | Section 1                                                                                                           | The ST reference is in Section 1.1, the TOE reference in Section 1.3, the TOE overview and description in Section 1.6.                                                                                                                             |

|                                 | ASE_OBJ.1 Security requirements for the operational environment | Section 2                                                                                                           | The objectives for the operational environment in Section 2 refer to the guidance documents.                                                                                                                                                       |

|                                 | ASE_REQ.3 Listed security requirements                          | Section 3                                                                                                           | All SFRs in this ST are taken from [2]. SFR "Verification of Platform Identity" is included. SFR "Secure Update of Platform is included". The SARs are an exact SESIP assurance level. No multiple assurance level is claimed.                     |

|                                 | ASE_TSS.1 TOE Summary Specification                             | Section 3                                                                                                           | All SFRs are listed per definition, and for each SFR the implementation and verification are defined in the SFR.                                                                                                                                   |

| ADV: Development                | ADV_FSP.4 Complete functional specifications                    | Section 1.4                                                                                                         | The evaluator will determine whether the provided evidence is suitable to meet the requirement.                                                                                                                                                    |

| AGD: Guidance documents         | AGD_OPE.1 Operational user guidance                             | Section 1.4                                                                                                         | The evaluator will determine whether the provided evidence is suitable to meet the requirement.                                                                                                                                                    |

|                                 | AGD_PRE.1 Preparative procedures                                | Section 1.4                                                                                                         | The evaluator will determine whether the provided evidence is suitable to meet the requirement.                                                                                                                                                    |

| ALC: Life-cycle support         | ALC_FLR.2 Flaw reporting procedures                             | Section 3.1.1                                                                                                       | The flaw reporting and remediation procedure is described.                                                                                                                                                                                         |

| ATE: Test                       | ATE_IND.1 Independent testing: conformance                      | Material provided to evaluator.                                                                                     | The evaluator will determine whether the provided evidence is suitable to meet the requirement.                                                                                                                                                    |

| AVA: Vulnerability assessment   | AVA_VAN.2 Vulnerability analysis                                | N.A. A vulnerability analysis is performed by the evaluator to ascertain the presence of potential vulnerabilities. | The evaluator performs penetration testing, to confirm that the potential vulnerabilities cannot be exploited in the operational environment for the TOE. Penetration testing is performed by the evaluator assuming an attack potential of Basic. |

# 4.2 SESIP Profile Conformance Mapping

This section provides rationales of conformance claimed in Section 1.2

**SESIP Security Target**

Table 11. SESIP Profile for Secure MCUs and MPUs Sufficiency

| Package Claimed    | Security Functional Requirements                    | Covered By      |

|--------------------|-----------------------------------------------------|-----------------|

| Base               | Verification of Platform Identity                   | Section 3.3.1.1 |

|                    | Secure Initialization of Platform                   | Section 3.3.1.5 |

|                    | Secure Updated of Platform                          | Section 3.3.2.1 |

|                    | Residual Information Purging                        | Section 3.3.5.3 |

|                    | Secure Debugging                                    | Section 3.3.5.5 |

| Security Services  | Cryptographic Operation                             | Section 3.3.4.1 |

|                    | Cryptographic Key Generation                        | Section 3.3.4.2 |

|                    | Cryptographic KeyStore                              | Section 3.3.4.3 |

|                    | Cryptographic Random Number Generation              | Section 3.3.4.4 |

| Software Isolation | Software Attacker Resistance: Isolation of Platform | Section 3.3.3.2 |

# 4.3 Cybersecurity Assurance Level 4 (CAL4) Sufficiency Rationales (Informative)

This section provides the informative CAL4 sufficiency rational as introduced in Annex E of ISO/SAE 21434:2021 Road vehicles - cybersecurity engineering [14], where four levels of Cybersecurity Assurance Level (CAL) is described, and CAL4 is the highest level. Given the fact that the annex in [14] is informative and only examples are provided without rigorous definition, this section can only provide demonstration on how this SESIP evaluation can help to meet the requirements of CAL4, rather than rigorous conformance analysis.

Also, this section only refers to the activities performed during this SESIP evaluation. NXP has deployed internal processes and procedures for product development and governance, not necessarily to have external evaluation or certification, to ensure ISO21434 compliance and they are certified as stated in <u>Section 3.2.1</u>. This section will not map NXP internal process and deliverables, but only to demonstrate the sufficiency from this SESIP evaluation. The following tables provide the requirements from Annex E of [14] and sufficiency rationals.

Table 12. Cybersecurity Assurance Level 4 (CAL4) expected rigour in cybersecurity assurance measures and sufficiency rationales

|                                                                                                      | CAL4 Requirement                                               | Covered by                                                                                                        | Rationale                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| a) Methods to provide confidence that cybersecurity activities are performed with appropriate rigour | All combinations of interactions between components are tested | Section 3.2.1,<br>SESIP<br>Methodology<br>and certification<br>scheme,<br>and AVA:<br>Vulnerability<br>assessment | The performance of cybersecurity activities are covered by this evaluation in several folds: As covered by the claim in Section 3.2.1, this evaluation verifies the ISO/SAE21434 certified process has applied to the product development. Furthermore, SESIP evaluation covers various cybersecurity actives. SESIP Methodology is of strong formalism as it is stated in the standard [2], and the certification scheme with lab and certifier setup further ensures that the certifier reviews the lab evaluation, and hence the evaluation meets the expected rigorous. For the testing coverage, the evaluated scope as illustrated in Figure 2 serves as a (sub)component for an embedded system inside a road vehicle. The security evaluation activities performed by an independent evaluator includes a review of the SAF85xx critical code (boot ROM, HSE Firmware), a vulnerability analysis, and penetration testing. Fuzz testing is part of the penetration testing that the evaluator can decide to apply based on its independent |

**SESIP Security Target**

Table 12. Cybersecurity Assurance Level 4 (CAL4) expected rigour in cybersecurity assurance measures and sufficiency rationales...continued

|                                                                                                                            | CAL4 Requirement                                                                                                                                               | Covered by                                          | Rationale                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                            |                                                                                                                                                                |                                                     | vulnerability analysis. Fuzzing with random vectors has been applied on other products of the same family without reveling any issue.                                           |

| b) Methods to<br>provide confidence<br>that unmanaged<br>vulnerabilities do<br>not remain                                  | Activities such as analysis and/or testing to search for vulnerabilities by exploratory methods                                                                | AVA:<br>Vulnerability<br>assessment                 | Vulnerability assessment and further on penetration testing required by SESIP AVA assurance components are of exploratory nature.                                               |

| c) Independence<br>scheme to provide<br>confidence that<br>the cybersecurity<br>activities<br>performed are<br>appropriate | Cybersecurity assessments are carried out by a person who is independent regarding management, resources and release authority from the originating department | SESIP<br>Methodology<br>and certification<br>scheme | SESIP Methodology by nature is carried out by 3rd party evaluator and another 3rd party certifier further verifies the compliance to the methodology for the SESIP scheme used. |

Table 13. Example of level of independence of cybersecurity activities and sufficiency rationales

| Activity                                                         | CAL4<br>Requireme | Definition of required level                                                                                                                                                                         | Covered by                                                           | Rationale                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Verification of cybersecurity concept and design activities      | 12                | The activity is performed by a person who is independent from the team that is responsible for the creation of the considered work product(s), i.e.                                                  | ASE: Security target<br>evaluation, and ADV:<br>Development          | The covered by column provides the corresponding activities in SESIP evaluation that map into ISO/SAE21434 activities. SESIP Methodology by nature is carried out by 3rd party evaluator and another 3rd party certifier further verifies the compliance to the methodology for the |

| Verification of the implementation and integration of components |                   | by a person reporting to a different direct superior.                                                                                                                                                | ATE: Test                                                            |                                                                                                                                                                                                                                                                                     |

| Cybersecurity validation                                         |                   |                                                                                                                                                                                                      | SESIP evaluation process, particularly AVA: Vulnerability assessment |                                                                                                                                                                                                                                                                                     |

| Cybersecurity assessment                                         | 13                | The activity is performed by a person who is independent, regarding management, resources and release authority, from the department responsible for the creation of the considered work product(s). | SESIP evaluation process and certification scheme setup              | SESIP scheme used.                                                                                                                                                                                                                                                                  |

Table 14. Example of parameters of testing methods and sufficiency rationales

| Activity           | CAL4<br>Requirement | -                                                         | Covered by this evaluation | Rationale                                                                                                |

|--------------------|---------------------|-----------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------|

| Functional testing |                     | based on requirements and interactions between components |                            | The ATE component is for functional testing, and it is based on the requirements on this security target |

**SESIP Security Target**

Table 14. Example of parameters of testing methods and sufficiency rationales...continued

| Activity                  | CAL4<br>Requirement | Definition of required level                                                                     | Covered by this evaluation                          | Rationale                                                                                                                                                                                             |

|---------------------------|---------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vulnerability<br>scanning | T1                  | for known vulnerabilities                                                                        | AVA:<br>Vulnerability<br>assessment                 | Scanning for known vulnerabilities is mandated for the scheme used                                                                                                                                    |

| Fuzz testing              | T2                  | with an increased number of test case iterations and/or adaptive selection of inputs             | AVA:<br>Vulnerability<br>assessment                 | Fuzz testing is part of the penetration testing that the evaluator can decide to apply based on its independent vulnerability analysis.                                                               |

| Penetration testing       | T2                  | assuming higher attacker<br>expertise, knowledge of the<br>item or component and/or<br>resources | ADV: Development, and AVA: Vulnerability assessment | The evaluator selected is well recognized in the industry and further vouched by the scheme used. NXP provided full software source code to the evaluator even this is not mandated for SESIP2 level. |

# 5 Bibliography

#### 5.1 Evaluation Documents

- [1] Security Evaluation Standard for IoT Platforms (SESIP), CEN, EN 17927:2023.

- [2] GlobalPlatform Technology Security Evaluation Standard for IoT Platforms (SESIP), version 1.2, GP\_FST\_070.

- [3] GlobalPlatform Technology SESIP Profile for Secure MCUs and MPUs, Version 1.0, GPT\_SPE\_150.

#### 5.2 Developer Documents

- [4] S32Z2 Data Sheet, Rev 3, NXP Semiconductors, April 2024.

- [5] S32ZE Security Overview, NXP Semiconductors, Feb 2023.

- [6] S32Z2 Reference Manual S32Z27RM, NXP Semiconductors; Rev. 4, 2024-12-10

- [7] HSE Service API Reference Manual for S32ZE, v0.2.58.0, NXP Semiconductors, Feb 2025.

- [8] AN649711, Selecting and using cryptographic algorithms and protocols, Rev 1.1, NXP Semiconductors, 16 February 2024.

- [9] HSE H/M Firmware Reference Manual, HSEFWRM, Rev 2.6, NXP Semiconductors, March 2025.

#### 5.3 Standards

- [10] J. Aumasson, et al, SipHash: A Fast Short-Input PRF, Progress in Cryptography INDOCRYPT 2012, pp 489-508.

- [11] Specification of Secure Hardware Extensions, Release R19-11, AUTOSAR, 2019.

- [12] W. Diffie and M Hellman, New Directions in Cryptography, IEEE Transactions on Information Theory. 22 (6): 644–654.

- [13] NIST SP 800-90A, Recommendation for Random Number Generation Using Deterministic Random Bit Generators, National Institute of Standards and Technology, January 2012.

- [14] ISO/SAE 21434:2021 Road vehicles cybersecurity engineering, edition 1.0, 2021, ISO/SAE.

**SESIP Security Target**

# **Legal information**

#### **Definitions**

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.