# **Certification Report**

## NXP SN300 B5 Series - Secure Element version SN300\_SE B5.1.002 JD

Sponsor and developer: NXP Semiconductors Germany GmbH Beiersdorfstraße 12 22529 Hamburg Germany

Evaluation facility:

*TÜV Informationstechnik GmbH* Am TÜV 1 45307 Essen Germany

Report number: NSCIB-CC-2300083-02-CR

1

Report version:

Project number: NSCIB-2300083-02

Author(s): Wim Ton

Date: 10 February 2025

Number of pages: 12

Number of appendices: 0

Reproduction of this report is authorised only if the report is reproduced in its entirety.

<u>Registered address</u>: Van den Berghlaan 48, 2132 AT Hoofddorp, The Netherlands nscib@trustcb.com https://trustcb.com/common-criteria/nscib/ https://nscib.nl TrustCB B.V. is a registered company at the Netherlands Chamber of Commerce (KVK), under number 858360275.

# CONTENTS

| Foreword                                                                                                                                                                   | 3                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Recognition of the Certificate                                                                                                                                             | 4                     |

| International recognition<br>European recognition                                                                                                                          |                       |

| 1 Executive Summary                                                                                                                                                        | 5                     |

| 2 Certification Results                                                                                                                                                    | 6                     |

| <ul> <li>2.1 Identification of Target of Evaluation</li> <li>2.2 Security Policy</li> <li>2.3 Assumptions and Clarification of Scope</li> <li>2.3.1 Assumptions</li> </ul> | 6<br>6<br>7<br>7      |

| 2.3.2 Clarification of scope                                                                                                                                               | 7                     |

| <ul> <li>2.4 Architectural Information</li> <li>2.5 Documentation</li> <li>2.6 IT Product Testing</li> <li>2.6.1 Testing approach and depth</li> </ul>                     | 7<br>8<br>8<br>8<br>8 |

| 2.6.2 Independent penetration testing                                                                                                                                      | 9                     |

| 2.6.3 Test configuration                                                                                                                                                   | 9                     |

| 2.6.4 Test results                                                                                                                                                         | 9                     |

| <ul> <li>2.7 Reused Evaluation Results</li> <li>2.8 Evaluated Configuration</li> <li>2.9 Evaluation Results</li> <li>2.10 Comments/Recommendations</li> </ul>              | 9<br>10<br>10<br>10   |

| 3 Security Target                                                                                                                                                          | 11                    |

| 4 Definitions                                                                                                                                                              | 11                    |

| 5 Bibliography                                                                                                                                                             | 12                    |

## Foreword

The Netherlands Scheme for Certification in the Area of IT Security (NSCIB) provides a third-party evaluation and certification service for determining the trustworthiness of Information Technology (IT) security products. Under this NSCIB, TrustCB B.V. has the task of issuing certificates for IT security products, as well as for protection profiles and sites.

Part of the procedure is the technical examination (evaluation) of the product, protection profile or site according to the Common Criteria assessment guidelines published by the NSCIB. Evaluations are performed by an IT Security Evaluation Facility (ITSEF) under the oversight of the NSCIB Certification Body, which is operated by TrustCB B.V. in cooperation with the Ministry of the Interior and Kingdom Relations.

An ITSEF in the Netherlands is a commercial facility that has been licensed by TrustCB B.V. to perform Common Criteria evaluations; a significant requirement for such a licence is accreditation to the requirements of ISO Standard 17025 "General requirements for the accreditation of calibration and testing laboratories".

By awarding a Common Criteria certificate, TrustCB B.V. asserts that the product or site complies with the security requirements specified in the associated (site) security target, or that the protection profile (PP) complies with the requirements for PP evaluation specified in the Common Criteria for Information Security Evaluation. A (site) security target is a requirements specification document that defines the scope of the evaluation activities.

The consumer should review the (site) security target or protection profile, in addition to this certification report, to gain an understanding of any assumptions made during the evaluation, the IT product's intended environment, its security requirements, and the level of confidence (i.e., the evaluation assurance level) that the product or site satisfies the security requirements stated in the (site) security target.

Reproduction of this report is authorised only if the report is reproduced in its entirety.

## **Recognition of the Certificate**

Presence of the Common Criteria Recognition Arrangement (CCRA) and the SOG-IS logos on the certificate indicates that this certificate is issued in accordance with the provisions of the CCRA and the SOG-IS Mutual Recognition Agreement (SOG-IS MRA) and will be recognised by the participating nations.

#### International recognition

The CCRA was signed by the Netherlands in May 2000 and provides mutual recognition of certificates based on the Common Criteria (CC). Since September 2014 the CCRA has been updated to provide mutual recognition of certificates based on cPPs (exact use) or STs with evaluation assurance components up to and including EAL2+ALC\_FLR.

For details of the current list of signatory nations and approved certification schemes, see <u>http://www.commoncriteriaportal.org</u>.

#### **European recognition**

The SOG-IS MRA Version 3, effective since April 2010, provides mutual recognition in Europe of Common Criteria and ITSEC certificates at a basic evaluation level for all products. A higher recognition level for evaluation levels beyond EAL4 (respectively E3-basic) is provided for products related to specific technical domains. This agreement was signed initially by Finland, France, Germany, The Netherlands, Norway, Spain, Sweden and the United Kingdom. Italy joined the SOG-IS MRA in December 2010.

For details of the current list of signatory nations, approved certification schemes and the list of technical domains for which the higher recognition applies, see <u>https://www.sogis.eu</u>.

## **1** Executive Summary

This Certification Report states the outcome of the Common Criteria security evaluation of the NXP SN300 B5 Series - Secure Element version SN300\_SE B5.1.002 JD. The developer of the NXP SN300 B5 Series - Secure Element version SN300\_SE B5.1.002 JD is NXP Semiconductors Germany GmbH located in Hamburg, Germany and they also act as the sponsor of the evaluation and certification. A Certification Report is intended to assist prospective consumers when judging the suitability of the IT security properties of the product for their particular requirements.

The TOE is a Security Integrated Circuit Platform for operating systems and applications with high security requirements.

The TOE incorporates a high frequency clocked ARM Cortex M33 processor augmented with its dedicated coprocessor for symmetric cryptography (SYM-lite), a secure copy machine (SMA), a Public-Key Cryptography (PKC) coprocessor, and a random number generator.

On-chip memories are Flash memory, ROM and RAMs. The ROM contains the IC dedicated software for factory testing, program upload, and the flash memory drivers.

In addition, the hardware embeds sensors which ensure the proper operating conditions of the device. Integrity protection of data and code involves error correction and error detection codes, EMFI detector, light sensing and other security functionality. Memory encryption and masking mechanisms are implemented to preserve the confidentiality of the stored data. The IC hardware is shielded against physical attacks. And the "lockstep" (redundant) CPU provides protection against faults in the CPU.

The TOE has been evaluated by TÜV Informationstechnik GmbH located in Essen, Germany. The evaluation was completed on 2025-02-10 with the approval of the ETR. The certification procedure has been conducted in accordance with the provisions of the Netherlands Scheme for Certification in the Area of IT Security *[NSCIB]*.

The scope of the evaluation is defined by the security target *[ST]*, which identifies assumptions made during the evaluation, the intended environment for the NXP SN300 B5 Series - Secure Element version SN300\_SE B5.1.002 JD, the security requirements, and the level of confidence (evaluation assurance level) at which the product is intended to satisfy the security requirements. Consumers of the NXP SN300 B5 Series - Secure Element version SN300\_SE B5.1.002 JD are advised to verify that their own environment is consistent with the security target, and to give due consideration to the comments, observations and recommendations in this certification report.

The results documented in the evaluation technical report *[ETR]*<sup>1</sup> for this product provide sufficient evidence that the TOE meets the EAL6 augmented (EAL6+) assurance requirements for the evaluated security functionality. This assurance level is augmented with ALC\_FLR.1 (Basic flaw remediation) and ASE\_TSS.2 (TOE summary specification with architectural design summary).

The evaluation was conducted using the Common Methodology for Information Technology Security Evaluation, Version 3.1 Revision 5 *[CEM]* for conformance to the Common Criteria for Information Technology Security Evaluation, Version 3.1 Revision 5 *[CC]* (Parts I, II and III).

TrustCB B.V., as the NSCIB Certification Body, declares that the evaluation meets all the conditions for international recognition of Common Criteria Certificates and that the product will be listed on the NSCIB Certified Products list. Note that the certification results apply only to the specific version of the product as evaluated.

The TOE was re-evaluated because of the update of the certificates of the production- and development sites. Neither the TOE nor the guidance has changed compared to version 01.

<sup>&</sup>lt;sup>1</sup> The Evaluation Technical Report contains information proprietary to the developer and/or the evaluator, and is not available for public review.

# 2 Certification Results

### 2.1 Identification of Target of Evaluation

The Target of Evaluation (TOE) for this evaluation is the NXP SN300 B5 Series - Secure Element version SN300\_SE B5.1.002 JD from NXP Semiconductors Germany GmbH located in Hamburg, Germany.

The TOE is comprised of the following main components:

| Delivery<br>item type                 | Identifier                           | Version     |

|---------------------------------------|--------------------------------------|-------------|

| Hardware                              | NXP SN300 B5 Series - Secure Element | B5.1.002 JD |

| IC<br>dedicated<br>software<br>in ROM | FactoryOS                            | 4.0.2       |

|                                       | BootOS                               | 4.0.3       |

|                                       | Flash Driver Software                | 2.4.5       |

To ensure secure usage a set of guidance documents is provided, together with the NXP SN300 B5 Series - Secure Element version SN300\_SE B5.1.002 JD. For details, see section 2.5 "Documentation" of this report.

For a detailed and precise description of the TOE lifecycle, see the [ST], Chapter 1.3.3.

### 2.2 Security Policy

The TOE maintains:

- the integrity and confidentiality of code and data stored in its memories;

- the different CPU modes with the related capabilities for configuration and memory access;

- the integrity, the correct operation and the confidentiality of security functionality provided by the TOE.

This is ensured by the construction of the TOE and its security functionality.

The TOE provides a hardware platform for an implementation of a smartcard application with:

- hardware to perform computations on multi-precision integers, which are suitable for public-key cryptography

- hardware to provide True Random Numbers

- memory management control;

- an ISO/IEC 7816 contact interface with UART.

- Serial Peripheral Interface (SPI)

- 2x I<sup>2</sup>C interfaces

- I<sup>3</sup>C interface (shared pins with second I<sup>2</sup>C interface)

- SPMI Interface

- GPIO interface by use of Special Function Registers

## 2.3 Assumptions and Clarification of Scope

#### 2.3.1 Assumptions

The assumptions defined in the Security Target are not covered by the TOE itself. These aspects lead to specific Security Objectives to be fulfilled by the TOE-Environment. For detailed information on the security objectives that must be fulfilled by the TOE environment, see section 4.2 of the *[ST]*.

#### 2.3.2 Clarification of scope

The evaluation did not reveal any threats to the TOE that are not countered by the evaluated security functions of the product.

The secure operation of cryptographic functionality in 2.2 requires a Cryptographic Library which is not part of this TOE. Therefore, Security Services and Security Features using this cryptographic functionality need to be evaluated in the composite product together with Cryptographic Library as part of the Security IC Embedded Software. As a consequence, for the Cryptographic Functionality, the scope of this evaluation is confined to protection against physical manipulation.

## 2.4 Architectural Information

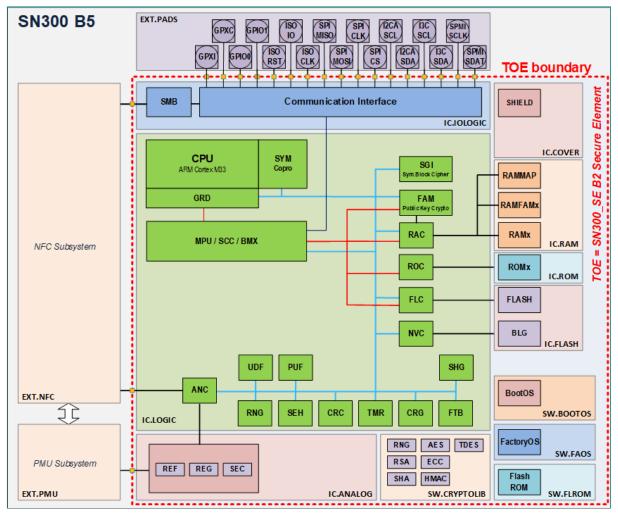

#### Figure 1 TOE Architecture

The TOE contains two separate busses. One peripheral control bus is provided for I/O communication. The secure peripheral bus serves protected internal communication.

The TOE implements a complex security functionality to protect code and data during processing and while stored to the device. This includes appropriate memory encryptions and masking schemes to preserve confidentiality.

Error detection codes (the Flash Secure Fetch Plus) are used to protect the integrity and manifold light sensing with EMFI detector are integrated to detect perturbations which could lead to integrity violation.

The "CPU Guard" detects errors in the program execution, and the memory protection separates the memory spaces of the various applications.

Active shielding is present and the operating conditions are monitored by sensors for the temperature, power supplies and frequencies.

#### 2.5 Documentation

The following documentation is provided with the product by the developer to the customer:

| Identifier                                                               | Version |

|--------------------------------------------------------------------------|---------|

| SN300_SE Information on Guidance and Operation                           | 0.4     |

| SN300V2, R2; Single Chip Secured (NFC) controller, Product data sheet    | 1.8     |

| SN300V2 TOE Identification (for B5.1.002), Data sheet addendum           | 0.1     |

| SN300_SE Programmer's Manual (for revision Bx), Application Note AN12729 | 0.7     |

| ARM® Cortex®-M33 Processor Technical Reference Material                  | r1p0    |

### 2.6 IT Product Testing

Testing (depth, coverage, functional tests, independent testing): The evaluators examined the developer's testing activities documentation and verified that the developer has met their testing responsibilities.

#### 2.6.1 Testing approach and depth

The developers' testing effort can be summarised in the following aspects.

TOE test configuration:

Functional tests have been performed by the evaluator on the TOE as part of the penetration testing. Additionally, developer tests performed on emulators and simulators have been reviewed.

Developer's testing approach:

All TSFs and related security mechanisms, subsystems and modules are tested in order to assure complete coverage of all SFRs.

Different classes of tests are performed to test the TOE in a sufficient manner.

- Verification Testing during Development:

- · Simulation tests (tool based and on FPGA),

- Validation of key parameters before tape-out.

- Evaluation and Characterization Testing on Silicon:

- Evaluation Testing to confirm results from Verification Testing (see above),

- Characterization testing over process, voltage and temperature (PVT) after Evaluation Testing.

- Characterization Testing during production under PVT conditions.

- Production Testing of each produced sample.

The developer testing reaches a code coverage of over 98% on the flash software. Boot OS and factory OS have a code coverage of 90-94%. A rationale has been given for the missing coverage.

#### 2.6.2 Independent penetration testing

The vulnerability analysis used know public vulnerabilities, [JIL-AM], and the findings from ADV\_IMP.

Some test results are reused from previous evaluations of the same hardware. The new test evaluate some additional functions of previously tested sub-systems.

| Certification ID | Leakage testing | Fault testing  | Logical testing |

|------------------|-----------------|----------------|-----------------|

| 2300083-02       | 7 person days   | 6 person days  | -               |

| 2300030-02       | 7 person days   | 12 person days | 5 person days   |

| 2300031-01       | -               | 4 person days  | -               |

| TOTAL            | 14 person days  | 22 person days | 5 person days   |

Perturbation used light and EMFI.

Information leakage was measured from power consumption and EM radiation.

The total test effort expended by the evaluators was 6 weeks. During that test campaign, 53% of the total time was spent on Perturbation attacks, 34% on side-channel testing, and 13% on logical tests.

#### 2.6.3 Test configuration

The tests are performed with the chip NXP SN300 B5 Series - Secure Element. The evaluated TOE is the silicon chip with its Dedicated Software.

The TOE is a "generic" device, i.e., a chip without any ROM embedded software.

All details about test items and their configurations, test equipment as well as detailed test descriptions are provided in the test reports of the ITSEF listed in Section 14.

The TOE submitted to evaluation does comprise a specific application. The Java Card Operating system JCOP is running on the chip and all testing needs to be performed trough the Operation system. The evaluator can only change applets that run on top of the operating system. For some special test cases (e.g. random number testing) a special version of the operating system was provided to allow access to raw random data. The operating system is not evaluated: it is out of the evaluation perimeter (i.e., no vulnerability analysis is performed on it).

#### 2.6.4 Test results

The testing activities, including configurations, procedures, test cases, expected results and observed results are summarised in the *[ETR*], with references to the documents containing the full details.

The developer's tests and the independent functional tests produced the expected results, giving assurance that the TOE behaves as specified in its [ST] and functional specification.

No exploitable vulnerabilities were found with the independent penetration tests.

For composite evaluations, please consult the [ETRfC] for details.

### 2.7 Reused Evaluation Results

There has been extensive reuse of the ALC aspects for the sites involved in the development and production of the TOE, by use of 28 site certificates and/or Site Technical Audit Reports.

The manufacturer tests have been reused in this evaluation.

Independent testing for which no new vulnerabilities and no improved techniques were known has been reused.

No sites have been visited as part of this evaluation.

## 2.8 Evaluated Configuration

The TOE is defined uniquely by its name and version number NXP SN300 B5 Series - Secure Element version SN300\_SE B5.1.002 JD.

### 2.9 Evaluation Results

The evaluation lab documented their evaluation results in the *[ETR]*, which references an ASE Intermediate Report and other evaluator documents, and Site Technical Audit Reports for the sites involved in the design and the production of the TOE. To support composite evaluations according to *[COMP]* a derived document *[ETRfC]* was provided and approved. This document provides details of the TOE evaluation that must be considered when this TOE is used as platform in a composite evaluation.

The verdict of each claimed assurance requirement is "Pass".

Based on the above evaluation results the evaluation lab concluded the NXP SN300 B5 Series -Secure Element version SN300\_SE B5.1.002 JD, to be **CC Part 2 extended, CC Part 3 conformant**, and to meet the requirements of **EAL 6 augmented with ALC\_FLR.1 and ASE\_TSS.2**. This implies that the product satisfies the security requirements specified in Security Target *[ST]*.

The Security Target claims 'strict' conformance to the Protection Profile [PP].

#### 2.10 Comments/Recommendations

The user guidance as outlined in section 2.5 "Documentation" contains necessary information about the usage of the TOE.

Certain aspects of the TOE's security functionality, in particular the countermeasures against attacks, depend on accurate conformance to the user guidance of both the software and the hardware part of the TOE. There are no particular obligations or recommendations for the user apart from following the user guidance. Please note that the documents contain relevant details concerning the resistance against certain attacks.

The customer or user of the product shall consider the results of the certification within his system risk management process. For the evolution of attack methods and techniques to be covered, the customer should define the period of time until a re-assessment for the TOE is required and thus requested from the sponsor of the certificate.

# 3 Security Target

The NXP SN300 B5 Series - Secure Element - Security Target, Version 0.5,22 Aug 2023 [ST] is included here by reference.

Please note that, to satisfy the need for publication, a public version [ST-lite] has been created and verified according to [ST-SAN].

## 4 Definitions

This list of acronyms and definitions contains elements that are not already defined by the CC or CEM:

|         | , , , , , , , , , , , , , , , , , , ,                           |

|---------|-----------------------------------------------------------------|

| ]       | Information Technology                                          |

| ITSEF   | IT Security Evaluation Facility                                 |

| JIL     | Joint Interpretation Library                                    |

| NSCIB   | Netherlands Scheme for Certification in the area of IT Security |

| PP      | Protection Profile                                              |

| TOE     | Target of Evaluation                                            |

| ACL     | Access Control List                                             |

| AES     | Advanced Encryption Standard                                    |

| CBC     | Cipher Block Chaining (a block cipher mode of operation)        |

| CBC-MAC | Cipher Block Chaining Message Authentication Code               |

| DES     | Data Encryption Standard                                        |

| DFA     | Differential Fault Analysis                                     |

| EMA     | Electromagnetic Analysis                                        |

| ETR     | Evaluation Technical Report                                     |

| FPGA    | Field Programmable Gate Array                                   |

| IC      | Integrated Circuit                                              |

| JIL     | Joint Interpretation Library                                    |

| OS      | Operation System                                                |

| RNG     | Random Number Generator                                         |

| ROM     | Read Only Memory                                                |

| RSA     | Rivest-Shamir-Adleman Algorithm                                 |

| SPA/DPA | Simple/Differential Power Analysis                              |

| TRNG    | True Random Number Generator                                    |

|         |                                                                 |

# 5 Bibliography

This section lists all referenced documentation used as source material in the compilation of this report.

| [CC]      | Common Criteria for Information Technology Security Evaluation, Parts I, II and III, Version 3.1 Revision 5, April 2017                              |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| [CEM]     | Common Methodology for Information Technology Security Evaluation, Version 3.1 Revision 5, April 2017                                                |

| [COMP]    | Joint Interpretation Library, Composite product evaluation for Smart Cards and similar devices, Version 1.5.1, May 2018                              |

| [ETR]     | EVALUATION TECHNICAL REPORT SUMMARY (ETR SUMMARY), 2300083-02_ETR_250210_v2, Version 2, 10 February 2025                                             |

| [ETRfC]   | EVALUATION TECHNICAL REPORT FOR COMPOSITE EVALUATION (ETR COMP), 2300083-02_ETR-COMP_250210_v2, Version 2, 10 February 2025                          |

| [JIL-APS] | Application of Attack Potential to Smartcards and Similar Devices, Version 3.2.1, Feb 2024 (sensitive with controlled distribution)                  |

| [JIL-AMS] | Attack Methods for Smartcards and Similar Devices, Version 2.4, Jan 2020 (sensitive with controlled distribution)                                    |

| [NSCIB]   | Netherlands Scheme for Certification in the Area of IT Security, Version 2.6, 02 August 2022                                                         |

| [PP_0084] | Security IC Platform Protection Profile with Augmentation Packages, registered under the reference BSI-CC-PP-0084-2014, Version 1.0, 13 January 2014 |

| [ST]      | NXP SN300 B5 Series - Secure Element - Security Target, Version 0.5,22 Aug 2023                                                                      |

| [ST-Lite] | NXP SN300 B5 Series - Secure Element, Security Target Lite, Rev. 0.5, 22<br>Aug 2023                                                                 |

| [ST-SAN]  | ST sanitising for publication, CC Supporting Document CCDB-2006-04-004, April 2006                                                                   |

(This is the end of this report.)