**Evaluation document**

# **Document information**

| Information | Content                                                                                                                                                                                                          |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | SESIP, PSA, Security Target, RW61x, RW610, RW612                                                                                                                                                                 |

| Abstract    | Security target for evaluation of the RW61x developed and provided by NXP<br>Semiconductors, according to SESIP Assurance Level 3 (SESIP3) based on<br>SESIP methodology, version 1.1, and PSA Certified Level 3 |

# **Revision History**

| Rev. | Date            | Description            |

|------|-----------------|------------------------|

| 1.0  | 6 February 2024 | First released version |

Rev. 1.0 — 6 February 2024

# 1 Introduction

This Security Target describes the RW61x platform and the exact security properties of the platform that are evaluated against GlobalPlatform Technology Security Evaluation Standard for IoT Platforms (SESIP), version 1.1, SESIP Assurance Level 3 (SESIP3) [1].

# 1.1 ST Reference

RW61x, SESIP Security Target, Revision 1.0, NXP Semiconductors, 6 February 2024.

# 1.2 SESIP Profile Reference and Conformance Claims

| Table 1. | SESIP | <b>Profile for</b> | Secure | <b>MCUs</b> | and M | IPUs | Conformance | Claims |

|----------|-------|--------------------|--------|-------------|-------|------|-------------|--------|

|----------|-------|--------------------|--------|-------------|-------|------|-------------|--------|

| Reference       | Value                                                                                                                |

|-----------------|----------------------------------------------------------------------------------------------------------------------|

| SP Name         | GlobalPlatform Technology SESIP Profile for Secure MCUs and MPUs [2]                                                 |

| SP Version      | Version 1.0                                                                                                          |

| Assurance Claim | SESIP Assurance Level 3 (SESIP3)                                                                                     |

| Package Claim   | Base SP, Package Secure Services, Package Software Isolation, Package<br>Hardware Protection, Package Secure Enclave |

#### Table 2. SESIP Profile for PSA Certified Level 3 Conformance Claims

| Reference                       | Value                                       |

|---------------------------------|---------------------------------------------|

| SP Name                         | SESIP Profile for PSA Certified Level 3 [3] |

| SP Version                      | V1.0 REL 01                                 |

| Assurance Claim                 | SESIP Assurance Level 3 (SESIP3)            |

| Optional and<br>Additional SFRs | See Section 4.3                             |

# 1.3 Platform Reference

# RW61x

# Table 3. Platform Reference

| Reference                           | Value                                                   |                                       |  |

|-------------------------------------|---------------------------------------------------------|---------------------------------------|--|

| Platform Name and<br>Version        | See <u>Table 5</u>                                      |                                       |  |

| Platform Identification             | Chip name and version See IC hardware in <u>Table 5</u> |                                       |  |

|                                     | PSA-RoT name and version                                | See updatable platform RoT in Table 5 |  |

| Platform Type                       | Microcontroller platform for IoT applications           |                                       |  |

| Trusted Subsystem<br>Identification | See security enclave and its software in <u>Table 5</u> |                                       |  |

# 1.4 Included Guidance Documents

The following documents are included with the platform:

| Table 4. | Guidance | Documents |

|----------|----------|-----------|

|----------|----------|-----------|

| Document                 | Reference                                                                                            |

|--------------------------|------------------------------------------------------------------------------------------------------|

| User Manual              | UM11865, RW61x User Manual [4]                                                                       |

| User Manual              | UM11864, RW61x Crypto Subsystem [5]                                                                  |

| Reference Manual         | RM00278, RW610/RW612 Registers[6]                                                                    |

| Datasheet                | RW610, Wireless MCU with Integrated Wi-Fi 6 and Bluetooth<br>Low Energy 5.3 Data Sheet [7]           |

| Datasheet                | RW612, Wireless MCU with Integrated Wi-Fi 6 and Bluetooth<br>Low Energy 5.3 / 802.15.4Data Sheet [8] |

| SESIP Security Target    | RW61x, SESIP Security Target, Revision 1.0, NXP<br>Semiconductors, 6 February 2024.                  |

| API Reference Manual     | User Manual of Crypto Library Normal Secure (CLNS) [9]                                               |

| Application Note         | AN13813 Secure boot on RW61x [10]                                                                    |

| Application Note         | AN13814 Debug authentication on RW61x [11]                                                           |

| Application Note         | AN6259, Common Trust Provisioning Conceptional Overview [15]                                         |

| Application Note         | AN13023, Selecting and using cryptographic algorithms and protocols [14]                             |

| Software Development Kit | RW61x SDK with TF-M v1.7 ported [12]                                                                 |

| Tool User Guidance       | Secure Provisioning SDK (SPSDK) Application User Guides [13]                                         |

| Reference Manual         | ARM Platform Security Architecture Firmware Framework 1.0 [19]                                       |

| Reference Manual         | ARM Firmware Framework for M 1.1 Extensions [20]                                                     |

| API Reference Manual     | PSA Attestation API 1.0 [21]                                                                         |

| API Reference Manual     | PSA Cryptography API 1.1 [22]                                                                        |

| API Reference Manual     | PSA Storage API 1.0 [23]                                                                             |

# **1.5 Platform Overview and Description**

The RW61x family is a highly integrated, low-power tri-radio Wireless MCU with an integrated MCU and Wi-Fi 6 + Bluetooth Low Energy (LE)  $5.3 / 802.15.4^{1}$  radios designed for a broad array of applications. Applications include connected smart home devices, gaming controllers, enterprise and industrial automation, smart accessories, and smart energy.

The RW61x MCU subsystem includes a 260 MHz Arm<sup>®</sup> Cortex<sup>®</sup>-M33 core with TrustZone<sup>TM</sup>-M, 1.2 MB on-chip SRAM. The RW61x also includes a Quad SPI interface with high bandwidth, and an on-the-fly decryption engine for securely accessing off-chip XIP flash.

<sup>1</sup> Superset feature, availability depends on product part number ordered

The RW61x includes a full-featured 1x1 dual-band (2.4 GHz / 5 GHz) 20 MHz Wi-Fi 6 (802.11ax) subsystem bringing higher throughput, better network efficiency, lower latency, and improved range over previous generation Wi-Fi standards. The Bluetooth LE radio supports 2 Mbit/s high-speed data rate, long range and extended advertising as well as LE Audio for a better overall audio experience. The on-chip 802.15.4 radio can

support Thread mesh networking protocol.<sup>1</sup>

The RW61x is an ideal device for Matter applications running over Wi-Fi, Ethernet and/ or Thread. The RW61x can operate as a Matter Controller as well as Thread Border

Router.<sup>1</sup> This capability enables full Matter functionality for local and cloud-based control, and for monitoring of IoT products seamlessly across major ecosystems.

EdgeLock<sup>™</sup> security technology of NXP is incorporated, offering secure boot, secure debug, secure firmware updates, and secure life cycle management as well as hardware cryptography and Physically Unclonable Function (PUF) for secure key management.

The advanced design of the RW61x delivers tight integration, low power, and highly secure operation in a space- and cost-efficient wireless MCU requiring only a single 3.3 V power supply.

# **1.5.1 Platform Security Features**

RW61x employs a security subsystem, EdgeLock System S50 (ELS S50), which together with platform firmware provides the following security features:

- NXP EdgeLock<sup>™</sup> Assurance

- NXP EdgeLock 2GO Trust Provisioning

- Trusted execution environment (TEE) based on Arm TrustZone-M

- Hardware root of trust

- Hardware cryptography accelerators (symmetric, asymmetric, secure hash, KDF, etc.)

- True Random Number Generator (TRNG)

- Physically Unclonable Function (PUF)

- OTP-based device configuration and life cycle management

- Secure boot, software update and debug

- On-chip tamper detection for voltage level and glitch, temperature and reset

# 1.5.2 Platform Type

Processor with internal hardware isolation with Arm TrustZone technology, secure memory, and a secure subsystem.

# **1.5.3 Platform Physical Scope**

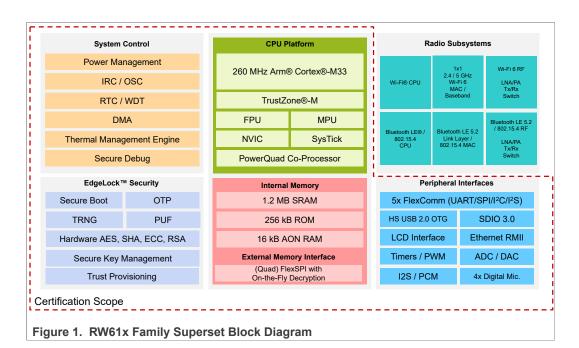

The physical scope is the part of RW61x microcontroller silicon chip as shown in Figure 1.

The hardware components and interfaces are listed in Chapter 1 of [7] and [8].

RW61x SESIP Security Target

# 1.5.4 Platform Logical Scope

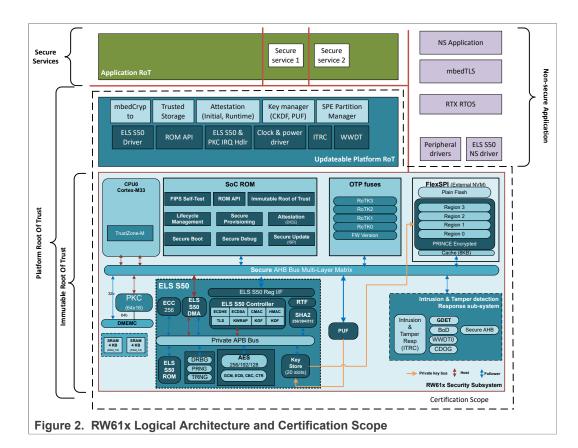

The logical scope includes the ROM firmware, and the optional flash loadable updatable platform root of trust (RoT) as illustrated in <u>Figure 2</u> and listed in <u>Table 5</u>. Any additional firmware, OS or application software stored on the platform is not in scope of this evaluation.

| Туре                         | Name                                       | Release                             | Form of delivery                        |

|------------------------------|--------------------------------------------|-------------------------------------|-----------------------------------------|

| IC Hardware and ROM Firmware | RW61x                                      | A1, A2                              | Silicon Chip and Onchip<br>ROM Firmware |

| ROM Firmware Patch           | RW61x ROM Patch                            | A1: 00120208<br>A2: 00210010        | Onchip Firmware                         |

| Security Enclave             | EdgeLock System S50<br>(ELS S50)           | 2.16.1                              | Onchip Hardware<br>Subsystem            |

| Security Enclave<br>Software | ELS S50 software<br>(microcode)            | 1.02.1                              | Onchip ROM Firmware                     |

| Updatable Platform<br>RoT    | RW61x SDK with TF-M<br>v1.7 ported         | 2.13.0 EAR4 TF-M<br>Secure Hardened | Software Package                        |

| Crypto Library               | Crypto Library Normal<br>Secure (CLNS) SDK | 1.3.0                               | Included in Software<br>Package         |

| Table 5. Platform Delivera | bles |

|----------------------------|------|

|----------------------------|------|

# RW61x

# **SESIP Security Target**

# 1.5.5 Required Non-Platform Hardware/Software/Firmware

RW61x has no internal flash, hence compatible external non-volatile memory shall be deployed via FlexSPI for image storage with sufficient size. See Chapters 4 of [4] for compatible external flash.

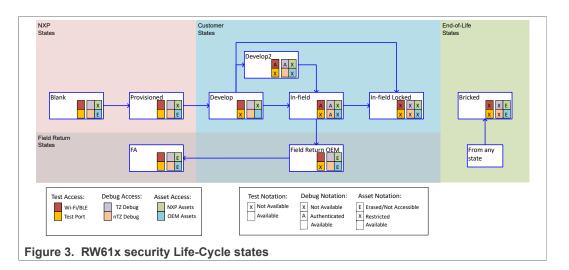

# 1.5.6 Life Cycle

This device supports a security Life-Cycle state model. The current Life-Cycle state determines the device functionality, debug and test port availability, and asset accessibility. The LC\_STATE fuse value controls the Life-Cycle state. The state values are selected so that additional fuse bits are burned to advance the state. Because fuses control the Life-Cycle state, moving to a more advanced state is an irreversible and permanent process. The Life-Cycle can only be advanced and cannot return to a previous state.

The boot ROM is responsible for checking the Life-Cycle state. Based on the Life-Cycle state, the ROM determines what boot flow is used, including whether control is passed to application code or not. The ROM also handles the opening of test and debug ports based on the Life-Cycle state. If the part is in the Bricked state or any invalid life cycle state, then the ROM will lock the part.

See more in Chapter 12 of [4].

RW61x

**SESIP Security Target**

# 1.5.7 Configurations

The MCU/MPU ensures the execution of platform trusted code, particularly the functions related to secure boot, updatability, and code isolation.

The security features discussed above are complemented by security services intended to be used by the higher software layers to implement a full-fledged Root of Trust and operating system

A Secure Enclave is used to fulfil the following security features as described in  $\underline{\text{Section}}$ 3.2.

# 1.5.8 Use Case

# [any user]

The product may be physically accessed by an unknown or untrusted user, in an environment where access to the product cannot be sufficiently controlled or even in a more hostile environment.

#### [any code]

It cannot be excluded that the product will execute code that is unknown to the product developer.

# 2 Security Objectives for the Operational Environment

# 2.1 Platform Objectives for the Operational Environment

For the platform to fulfill its security requirements, the operational environment (technical or procedural) <u>must</u> fulfill the following objectives:

| Description                                                                                                                                                                                                                                                                                                                                                                       | Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The operating system or application code are expected to verify the correct version of all platform components it depends on, as described in <u>Section 3.4.1.1</u> of this document.                                                                                                                                                                                            | Section 3.4.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| The operating system or application code are expected to make use of the Secure Boot feature as described in Chapter 10 of [4].                                                                                                                                                                                                                                                   | [ <u>10]</u> and Chapter<br>10 of [ <u>4]</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| The integrating environment is expected to configure the debug functionality as described in Chapter 13.7 of [4]. and [11] to meet the extra physical attacker resistance.                                                                                                                                                                                                        | [ <u>11]</u> and Chapter<br>13.7 of [ <u>4]</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Cryptographic keys and certificates outside of the Platform are subject to secure key management procedures.                                                                                                                                                                                                                                                                      | This document                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Actors in charge of platform management, for instance for signature of firmware update, are trusted.                                                                                                                                                                                                                                                                              | This document                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| The operating system or application code are expected to<br>ensure the correct version of the crypto library and SDK drivers<br>are integrated and configured.                                                                                                                                                                                                                    | This document                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| The operating system or application code are expected to<br>update an image with proper remedy solution and version<br>increased and/or revoke key in case of security incidence<br>occurrence of the image and/or the key.                                                                                                                                                       | Chapter 10 of [4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RW61x provides lifecycle states and secure mechanism of<br>lifecycle state transition according to the use case, and the<br>operational environment is expected to configure the platform<br>accordingly for lifecycle state transitions. In general, the<br>operating system or application code are expected to configure<br>the platform to In-field or in-field locked state. | Chapter 12 of [4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RW61x provides majorly two different isolation mechanisms:<br>S50 vs rest of SoC, and TF-M SPE vs NSPE based on Trust<br>Zone technology. The operating system or application code<br>are expected to configure and utilize these mechanisms for<br>isolation between platform and application.                                                                                   | Chapters 14 and<br>16 of [5], [19]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RW61x supports both CTR and GCM modes for PRINCE<br>external memory encryption. If memory integrity, authenticity,<br>and/or physical attacker resistance are in demand for the use<br>cases, the operating system or application code are expected to<br>configure the PRINCE to GCM mode.                                                                                       | Chapters 4.2.11<br>of of [4], and<br>Chapter 12 of [5]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| If local physical attack is applicable for the use cases, the<br>following configurations shall be kept after boot by the operating<br>system or application code:<br>• ITRC settings                                                                                                                                                                                             | Chapter 13 of [5],<br>[12]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                   | The operating system or application code are expected to verify<br>the correct version of all platform components it depends on, as<br>described in Section 3.4.1.1 of this document.<br>The operating system or application code are expected to make<br>use of the Secure Boot feature as described in Chapter 10 of<br>[4].<br>The integrating environment is expected to configure the debug<br>functionality as described in Chapter 13.7 of [4]. and [11] to<br>meet the extra physical attacker resistance.<br>Cryptographic keys and certificates outside of the Platform are<br>subject to secure key management procedures.<br>Actors in charge of platform management, for instance for<br>signature of firmware update, are trusted.<br>The operating system or application code are expected to<br>ensure the correct version of the crypto library and SDK drivers<br>are integrated and configured.<br>The operating system or application code are expected to<br>update an image with proper remedy solution and version<br>increased and/or revoke key in case of security incidence<br>occurrence of the image and/or the key.<br>RW61x provides lifecycle states and secure mechanism of<br>lifecycle state transition according to the use case, and the<br>operating system or application code are expected to configure<br>the platform to In-field or in-field locked state.<br>RW61x provides majorly two different isolation mechanisms:<br>S50 vs rest of SoC, and TF-M SPE vs NSPE based on Trust<br>Zone technology. The operating system or application.<br>RW61x supports both CTR and GCM modes for PRINCE<br>external memory encryption. If memory integrity, authenticity,<br>and/or physical attacker resistance are in demand for the use<br>cases, the operating system or application.<br>RW61x supports both CTR and GCM modes for PRINCE<br>external memory encryption. If memory integrity, authenticity,<br>and/or physical attacker resistance are in demand for the use<br>cases, the operating system or application code are expected to<br>configure the PRINCE to GCM mode.<br>If local physical attack is applicable for the use cases, the<br>following configurations shall be kept after |

Table 6. Platform Objectives for the Operational Environment

© 2024 NXP B.V. All rights reserved.

# **3** Security Requirements and Implementation

# 3.1 Security Assurance Requirements

The claimed assurance requirements package is: **SESIP Assurance Level 3 (SESIP3)** as defined in Chapter 4 of GlobalPlatform Technology Security Evaluation Standard for IoT Platforms (SESIP), version 1.1 [1].

# 3.1.1 Flaw Reporting Procedures (ALC\_FLR.2)

In accordance with the requirement for flaw reporting procedures (ALC\_FLR.2), the developer has defined the following procedure:

NXP has defined a Product Security Incident Response Process (PSIRP), implemented by a dedicated team (PSIRT). This process provides a publicly available interface (<u>https://nxp.com/psirt</u>), and includes four major steps:

- **Reporting**. The process begins when the PSIRT becomes aware of a potential security vulnerability in an NXP product. The reporter receives an acknowledgment and updates throughout the handling process.

- **Evaluation**. The PSIRT confirms the potential vulnerability, assesses the risk, determines the impact and assigns a processing priority. If the vulnerability is confirmed, the priority determines how the issue is handled throughout the remaining steps in the process.

- Solution. Working with PSIRT, the product team develops a solution that mitigates the reported security vulnerability. Solutions will take different forms based on the vulnerability. Because of the nature of NXP products mostly silicon products where the firmware is in ROM -, very often the solution can only be provided in a next version of the chips and the short-term solution will consist of recommending security measures to be applied in systems using the NXP product.

- **Communication**. As said above, because of the nature of the NXP products, the solution to systems using the affected products often needs to be found in additional countermeasures in those systems. The communication on the vulnerability and solutions will in most cases be done directly towards the affected customers. For previously unknown or unreported issues, NXP will acknowledge the reporter of the issues (unless the reporter requests otherwise).

The platform's Secure Boot feature is able to verify the authenticity of customer code during the initial boot and outside of the boot sequence, providing an appropriate mechanism for supporting the update of this code. The update mechanism is also supported in the loadable firmware of TF-M. See <u>Section 3.4.2.1</u> for further information.

# 3.2 Security Process Packages (SPPs)

This package is extended from SESIP draft version to the CEN Enquiry (prEN 17927:2022) by CEN/JTC 13.

# 3.2.1 Trust provisioning

A trust provisioning process ensures the secure management in a trusted environment of *assets in <u>Table 7</u>* and its/their loading into the platform for the following use cases *in <u>Table 7</u>* as specified in *reference in <u>Table 7</u>*.

**SESIP Security Target**

Both the trusted environment and the platform protect the *access, confidentiality, integrity* of provisioned data.

Table 7. Trust provisioning

| Assets             | Use Case                                | Reference |

|--------------------|-----------------------------------------|-----------|

| Cryptographic Keys | OEM Secure Provisioning                 | [15]      |

| Cryptographic Keys | EdgeLock 2GO                            | [15]      |

| Customer Data      | Customer Customized Provisioning by NXP | [15]      |

#### Conformance rationale:

Trust Provisioning (TP) describes the process of establishing a trust anchor in NXP devices that can be used by customers. This trust anchor could be a cryptographic key (or a set of keys), a unique identifier, or customer specific content. See more in [15], <u>Section 3.4.2.1</u> and <u>Section 3.4.4.2</u>.

# 3.3 Security Functional Requirements for Security Enclave

RW61x employ a security enclave: EdgeLock System S50 (ELS S50), which fulfills the following security functional requirements:

# 3.3.1 Identification and Attestation of Platforms and Applications

#### 3.3.1.1 Verification of Platform Identity

The platform provides a unique identification of the platform, including all its parts and their versions.

# Conformance rationale:

The ELS S50 version is available from ELS\_VERSION. The values shall match the versions indicated in <u>Table 5</u>. See more in Chapter 16.5.19 of [5].

# 3.3.2 Extra Attacker Resistance

# 3.3.2.1 Software Attacker Resistance: Isolation of Platform Parts

The platform provides isolation between platform parts, such that an attacker able to run code *in the platform parts outside of the Secure Enclave* can compromise neither the integrity and confidentiality of *the Secure Enclave* nor the provision of any other Security Functional Requirements.

#### Conformance rationale:

The ELS S50 module is a security subsystem supporting a wide range of cryptographic algorithms and providing strong key isolation from the rest of the system. When embedded in an SoC, ELS S50 serves as the main building block of the SoC's immutable Root of Trust. It is used as part of the trust anchor during secure boot, secure debug access, life-cycle management, and trust provisioning.

ELS S50 has its own controller and exclusive system resources with enforced access control, hence it is isolated from the rest of platform. See more in Chapter 16 of [5].

# 3.3.3 Cryptographic Functionality

# 3.3.3.1 Cryptographic Operation

The platform provides the application with operations in <u>Table 8</u> functionality with algorithms in Table 8 as specified in specifications in Table 8 for key lengths described in Table 8 and modes described in Table 8.

| Operation                                                   | Algorithm | Specification   | Key Lengths                     | Modes         |

|-------------------------------------------------------------|-----------|-----------------|---------------------------------|---------------|

| Encryption and decryption                                   | AES       | NIST FIPS 197   | 128, 192, 256 <sup>[1][2]</sup> | ECB, CBC, CTR |

| Authenticated<br>encryption,<br>authenticated<br>decryption | AES       | NIST SP 800-38d | 128, 192, 256 <sup>[1][2]</sup> | GCM           |

| Hashing                                                     | SHA2      | NIST FIPS 180-4 | 224, 256, 384, 512              | -             |

| MAC<br>generation and<br>verification                       | HMAC      | RFC2104         | Up to 512 <sup>[1][3]</sup>     | SHA-256       |

| MAC<br>generation and<br>verification                       | CMAC      | RFC4493         | 128, 256 <sup>[1][2]</sup>      | AES           |

| Signature<br>generation and<br>verification                 | ECDSA     | NIST FIPS 186-5 | 256                             | secp256r1     |

All key lengths supported by key stored in memory outside of ELS S50. ELS S50 keystore available for 128- and 256-bit keys. [1]

[2] [3]

ELS S50 keystore available for 256-bit keys.

### **Conformance rationale:**

The crypto coprocessors are located in ELS S50. ELS S50 provides the symmetric, hashing, and more functions. See more in Chapter 16 of [5]..

# 3.3.3.2 Cryptographic Key Generation

The platform provides the application with a way to generate cryptographic keys for use in algorithms in Table 9 as specified in specifications in Table 9 for key lengths described in Table 9

| ID      | Algorithm                     | Specification   | Key Lengths |

|---------|-------------------------------|-----------------|-------------|

| ECC     | ECC                           | ANSI X9.62      | 256         |

| HKDF    | HKDF                          | RFC5869         | 128, 256    |

| CKDF    | CKDF                          | NIST 800-108    | 128, 256    |

| TLS KDF | TLS Master Key<br>Derivation  | TLS1.2          | -           |

| TLS KDF | TLS Session Key<br>Derivation | TLS1.2          | -           |

| ECDH    | ECDH                          | NIST SP 800-56A | 256         |

Table 9. Cryptographic Key Generation

© 2024 NXP B.V. All rights reserved.

#### Conformance rationale:

The ELS S50 also provides key generation service. See more in Chapter 16.5.2 of [5].

#### 3.3.3.3 Cryptographic KeyStore

The platform provides the application with a way to store *cryptographic keys* such that not even the application can compromise the *authenticity, integrity, confidentiality* of this data. This data can be used for the cryptographic operations *encryption, decryption, signature generation, MAC generation, key derivation, shared secret generation.*

#### Conformance rationale:

ELS S50 provides key store function. Keys can be stored in ELS in a bank of internal 128-bit registers (each register is called a "key slot"). Specifically, their values (the key material) cannot be accessed by the system. Keys in KeyStore can be created by key exchange and key derivation functions in <u>Section 3.3.3.1</u>, key generation function in <u>Section 3.3.3.2</u>, unwrapping external RFC3394 wrapped key, or imported from unique key derivated from PUF. Each Keystore Key has associated properties and ELS S50 enforces usage rules based on the properties of keys. See more in Chapter 16.5.16 of [5].

### 3.3.3.4 Cryptographic Random Number Generation

The platform provides the application with a way based on *physical noise and DRBG* to generate random numbers to as specified in *NIST.SP.800-90B and NIST.SP.800-90A CTR-DRBG with AES-128*.

#### Conformance rationale:

ELS S50 has physical true random number generator and internal DRBG module as defined in NIST SP 800-90A. The TRNG archives NIST SP 800-90B compliance.

Furthermore:

• TRNG is capable to pass AIS 31 statistical tests T0-T8

See more in Chapters 16.5.6 of [5].

# 3.3.4 Compliance Functionality

# 3.3.4.1 Residual Information Purging

The platform ensures that *key store areas*, with the exception of *none*, is erased using the method specified in *Chapter 16.5.2.9 of [5]* before the memory is (re)used by the platform or application again and before an attacker can access it.

# Conformance rationale:

ELS S50 provide KDELETE command which removes the key and zeroize the register. See more in Chapter 16.5.2.9 of [5].

# 3.4 Security Functional Requirements for SoC

In the following Security Functional Requirements, the term **platform** covers the **RW61x physical and logical scope**, and the term **application** refer to any additional firmware, OS or application software which is out of evaluation scope. It represents a part of the final connected device.

RW61x fulfils the following security functional requirements:

# 3.4.1 Identification and Attestation of Platforms and Applications

#### 3.4.1.1 Verification of Platform Identity

The platform provides a unique identification of the platform, including all its parts and their versions.

#### Conformance rationale:

Besides reading out ELS S50 HW and driver version as introduced in <u>Section 3.3.1.1</u>, SoC Hardware and ROM identifier and revision number can be read from CHIP\_INFO register and one way to do so is to use GetProperty command in ISP mode as specified in Section 8.5.2 and 8.5.16 of [4] with tag 10h. The return value shall match to the value in Chapter 71.1.30 of [6] and the version shall match the value indicated in <u>Section 1.5.4</u>.

The ROM patch revision is stored in OTP fuse index 359, which can be read via ISP mode or ROM API, and the return value shall be the same as <u>Section 1.5.4</u>. See more in Sections 8.5.12 and 9.2.4 of [4].

The Updatable Platform RoT Firmware including TF-M ported are delivered in logical format as a software library. One can identified the version in readme file and verify the commit hash as defined in Section 1.5.4.

#### 3.4.1.2 Verification of Platform Instance Identity

The platform provides a unique identification of that specific instantiation of the platform, including all its parts and their versions.

# **Conformance rationale:**

The platform stores a 128-bit IETF RFC4122 compliant non-sequential Universally Unique Identifier (UUID). It can be read from the fuseword 46 onwards. Refer to Chapter 10.2.4.1 of [4].. One way to read out UUID is to use GetProperty command in ISP mode with tag 12h as specified in Chapter 8.5.2 and 8.5.16 of [4]..

# 3.4.1.3 Attestation of Platform Genuineness

The platform provides an attestation of the "Verification of Platform Identity" and "Verification of Platform Instance Identity", in a way that cannot be cloned or changed without detection.

#### Conformance rationale:

RW61x with TF-M Ported also supports the PSA attestation API to produce an initial attestation token in IETF EAT format containing measurements of the firmware, which provides an attestation service which reports on the device identity, firmware measurements and runtime state of the device. The attestation can be verified by remote entities. The tokens are signed using attestation keys stored in the internal flash. See more in [19] and [21].

#### 3.4.1.4 Attestation of Platform State

The platform provides an attestation of the state of the platform, such that it can be determined that the platform is in a known state.

#### Conformance rationale:

#### See Section 3.4.1.3.

#### 3.4.1.5 Secure Initialization of Platform

The platform ensures its authenticity and integrity during the platform initialization. If the platform authenticity or integrity cannot be ensured, the platform will go to *reset state*.

#### Conformance rationale:

The secure part of the ROM bootloader of RW61x provides secure boot operation.

Secure boot prevents unauthorized code from being executed on a given product. To ensure this level of security, secure boot always leaves the device ROM in an executing mode when coming out of a reset. The ROM can then assess the first user executable image resident in the external flash memory and determine the authenticity of that code. The control is transferred to authentic code only. A chain of trusted code from the ROM to the user boot code is established. And the chain can be further extended through the verification of digital signatures associated with additional code layers.

The Elliptic Curve Digital Signature Algorithm (ECDSA) is used in this architecture to verify the authenticity of the boot code. The boot code is always signed with ECDSA private keys, either based on P-256 or P-384. The corresponding ECDSA public keys used for signature verification (Root of Trust Keys) are contained in the certificate block included in the signed image. Support is provided for up to four Root of Trust keys.

The operating system or application code have the option to further enable built-in self-tests in Secure Boot ROM to ease the certification of NIST CMVP.

See more in Chapter 10 of [4]..

# 3.4.2 Product Lifecycle: Factory Reset / Install / Update / Decommission

#### 3.4.2.1 Secure Update of Platform

The platform can be updated to a newer version in the field such that the integrity, authenticity and confidentiality of the platform is maintained.

#### Conformance rationale:

The secure part of the ROM bootloader of RW61x provides secure firmware update operation.

Secure firmware updates perform an authentication of the new firmware prior to committing it to the memory. In this case, the chain of trust is extended from the old, currently executing code, to the new code.

Another use case for secure firmware update is to hide the application binary code during transit over public media such as the web. For this use case, the firmware update image is encrypted. As the new firmware is written into the device memory, it is decrypted.

In this architecture, both cases of secure firmware update are supported. The SB file format is encrypted and digitally signed. The SB file can be loaded via interfaces such as USB, and UART. Or the SB file can be provided to the ROM API as a complete binary file.

The anti-rollback is achieved by OTP fuseword. The OTP fusemap contains monotonic counters or ROTKH revocation fields that can be updated as these are implemented as redundant 16-bit fusewords. See more in Chapter 10 of [4]..

Furthermore, trust provisioned private key, together with other pre-installed key material, is then used for authentication and secure connection to the device, enabling secure provisioning of OEM assets even in the manufacturing environment OEM may not fully trust. See more in Sections 3.8.3, 4.1 and 4.2.2 of [15], and Section 3.2.1.

NXP further offers services to securely provision customer's data, keys and/or firmware in NXP trust provision process during product manufacture, and advance device life cycle state if needed. The customer data is unknown for this evaluation, hence it is out of scope. See more in Section 3.8.1 of [15], and Section 3.2.1.

# 3.4.2.2 Field Return of Platform

The platform can be returned to the vendor without user data.

# **Conformance rationale:**

The ROM on this device has an FA mode command (SET\_FA\_MODE). The command disables sensitive information (for example, rekeying of keys) before giving the device to OEM factory for fault analysis. The ROM allows the SET\_FA\_MODE command only when a corresponding flag in Debug\_State is set. Upon receiving the command ROM will program OTP fuseword (45) to set LifeCycle to Field Return OEM (0x1F) and triggers a sw reset.

The FA\_MODE sequence when activated by the boot ROM is:

- 1. Put PUF and ELS modules in FA mode.

- 2. Rekeys all the application usage keys including the memory encryption IPED keys.

- 3. Open all debug ports.

- 4. Enter while(1) loop.

This mechanism protects leakage of any residue data left during life-cycle state transition. It can further move to FA life cycle state if the device is being returned to NXP for testing and failure analysis, and further sensitive information is erased, and that is equivalent that all information protected by the application usage key is purged. See more in Chapters 12.6 and 13.7.6 of [4]..

# 3.4.2.3 Decommission of Platform

The platform can be decommissioned.

# Conformance rationale:

RW61x provides Bricked End-of-Life security life-cycle state. Customers or NXP can use this state to remove a device from regular use, and erase or block the access to secret information inside the device.

The Bricked state is the end-of-life state for the device, when a part is removed permanently from service. In this mode, the ROM locks up the device immediately on any reset. The debug and test mode ports are also disabled.

Bricked is the final life-cycle state. The device cannot be advanced to any other state from Bricked. Also all the keys stored in ELS S50, PUF derived data including die unique keys and the memory encryption IPED keys are permanently destroyed, hence the PUF derived data and IPED protected memory is equivalent to be purged. See more in Chapter 12.7 in [4].

# 3.4.3 Extra Attacker Resistance

#### 3.4.3.1 Physical Attack Resistance

The platform detects or prevents attacks by an attacker with physical access before the attacker compromises any of the functional requirements, ensuring that the functional requirements are not compromised.

#### Conformance rationale:

RW61x is equipped with Intrusion and Tamper Response Controller (ITRC). ITRC provides mechanism to configure the response action for an intrusion event detected by on-chip security sensors. Intrusion Response is the action a device performs in order to prevent misuse of the device or disclosure of critical assets (cryptographic keys, personal data) that are generated or stored within the device. The response mechanism is typically triggered by either a signal from an on-chip sensor designed to detect that the device is in a threat condition or by an explicit command provided by the software. See more in Chapter 13 of [5].

Also, the software components including ROM and TF-M ported leverage the code watchdog. For code watchdog, see more in Chapter 15 of [5]. The crypto coprocessor and the library are secure hardened against potential physical attacks. The TF-M ported further enables Fault Injection Hardening (FIH) library in the HIGH profile.

### 3.4.3.2 Software Attacker Resistance: Isolation of Platform (between SPE and NSPE)

The platform provides isolation between the application and itself, such that an attacker able to run code as an application on the platform cannot compromise any other claimed security functional requirements.

#### Conformance rationale:

There are multiple isolation features presented in the platform.

The ELS S50 isolation has been introduced in <u>Section 3.3</u>.

PRINCE-based memory encryption also ensures Secure Isolation between multiple IP vendors. Initial Vector (IV) is derived by secure-privilege and a different value is used for every independent memory region, ensuring the isolation between each other. See more in Chapters 7.3 and 7.4 of [4].

ARM TrustZone enables Secure Isolation during run-time by providing four distinct levels of privilege: secure-privilege, secure-user, non-secure-privilege, non-secureuser. Every peripheral is equipped with Peripheral Protection Checker (PPC) that can be programmed to control access to that peripheral, following the ARM TrustZone philosophy. Every memory is equipped with Memory Protection Checker (MPC) that can also be programmed in the same way as the PPC. Secure AHB Controller is in charge of programming all PPC and MPC blocks and only the highest level of privilege, which is secure-privilege, is allowed to do that. See more in Chapter 14 of [5]. PSA Level 2 Isolation supported by TF-M SPM using TrustZone and Secure MPU on v8-M cores [19].

# 3.4.3.3 Software Attacker Resistance: Isolation of Platform (between PSA-RoT and Application Root of Trust Services

The platform provides isolation between the application and itself, such that an attacker able to run code as an application on the platform cannot compromise any other claimed security functional requirements.

#### Conformance rationale:

RW61x

The isolation between PSA-RoT and Application Root of Trust Services is included in <u>Section 3.4.3.2</u>.

Also see more in <u>Section 3.4.4.4</u> about key isolation.

# 3.4.3.4 Software Attacker Resistance: Isolation of Platform Parts

See <u>Section 3.3.2.1</u>.

# 3.4.4 Cryptographic Functionality

# 3.4.4.1 Cryptographic Operation

The platform provides the application with *operations in <u>Table 8</u> and <u>Table 10</u> functionality with <i>algorithms in <u>Table 8</u> and <u>Table 10</u> as specified in <i>specifications in <u>Table 8</u> and <u>Table 10</u> for key lengths <i>described in <u>Table 8</u> and <u>Table 10</u> and modes <i>described in <u>Table 8</u> and <u>Table 8</u> and <u>Table 10</u>.*

| Operation                                   | Algorithm | Specification          | Key Lengths                                          | Modes                                |

|---------------------------------------------|-----------|------------------------|------------------------------------------------------|--------------------------------------|

| Signature<br>generation and<br>verification | EdDSA     | NIST FIPS 186-5        | 255                                                  | Ed25519                              |

| Signature<br>generation and                 | ECDSA     | NIST FIPS 186-5        | 192, 224, 256, 384,<br>521                           | secpXXXr1, XXX = key<br>length       |

| verification                                |           |                        | 192, 224, 256                                        | secpYYYk1, YYY = key<br>length       |

|                                             |           |                        | 160 <sup>[1]</sup> , 192, 224,<br>256, 320, 384, 512 | brainpoolPZZZr1, ZZZ<br>= key length |

| Signature<br>generation and<br>verification | RSA       | PKCS v1.15 and RSA PSS | 2048, 3072, 4096                                     | -                                    |

Table 10. Cryptographic Operations provided outside of ELS S50

[1] Refer to [14] for considerations on algorithm and key lengths.

#### Conformance rationale:

On top of ELS S50 security coprocessor introduced in <u>Section 3.3.3.3</u>, RW61x also deploys Public-Key Crypto Coprocessor (PKC, Chapter 18 of [5]). Crypto Library has been developed leveraging ELS S50 and PKC [9]. Part of supported algorithms are further enabled in the TF-M ported [22].

# 3.4.4.2 Cryptographic Operation (with provisioned key)

The platform provides the application with *operations in <u>Table 11</u>* functionality with *algorithms in <u>Table 11</u>* as specified in *specifications in <u>Table 11</u>* for key lengths *described in <u>Table 11</u>* and modes *described in <u>Table 11</u>*.

Table 11. Cryptographic Operations

| Operation               | Algorithm | Specification | Key Lengths | Modes      |

|-------------------------|-----------|---------------|-------------|------------|

| Signature<br>Generation | ECDSA     | ANSI X9.62    | 256         | NIST P-256 |

| Table 11. | Cryptographic | Operationscontinued |

|-----------|---------------|---------------------|

|-----------|---------------|---------------------|

| Operation         | Algorithm | Specification | Key Lengths | Modes |

|-------------------|-----------|---------------|-------------|-------|

| Key<br>unwrapping | AES       | RFC3394       | 256         | -     |

#### Conformance rationale:

The trust provisioning service also provide provision for EdgeLock 2GO root-of-trust keys, hence their cryptographic operations are available to the platform which can enable secure communication establishment with EdgeLock 2GO infrastructure and hence EdgeLock 2GO Services. See more in Section 4.6 of [15] and Section 3.2.1.

# 3.4.4.3 Cryptographic Key Generation

The platform provides the application with a way to generate cryptographic keys for use in *algorithms in <u>Table 9</u> and <u>Table 12</u> as specified in <i>specifications in <u>Table 9</u> and <u>Table 12</u> for key lengths <i>described in <u>Table 9</u> and <u>Table 12</u>.*

| ID   | Algorithm | Specification   | Key Lengths                                                                              |

|------|-----------|-----------------|------------------------------------------------------------------------------------------|

| AES  | AES       | NIST SP800-133  | 128, 192, 256                                                                            |

| ECC  | ECC       | ANSI X9.62      | 160, 192, 224, 255, 256, 320, 384,<br>512, 521                                           |

| RSA  | RSA       | PKCS#1          | 2048, 3072, 4096                                                                         |

| ECDH | ECDH      | NIST SP 800-56A | 255 (Curve25519), 448 (Curve448)                                                         |

|      |           |                 | 192, 224, 256, 384, 521 (secpXXXr1,<br>XXX = key length)                                 |

|      |           |                 | 192, 224, 256 (secpYYYk1, YYY = key length)                                              |

|      |           |                 | 160 <sup>[1]</sup> , 192, 224, 256, 320, 384, 512<br>(brainpoolPZZZr1, ZZZ = key length) |

Table 12. Cryptographic Key Generation

[1] Refer to [14] for considerations on algorithm and key lengths.

#### **Conformance rationale:**

The crypto library also provides key generation service leveraging the coprocessors. On top of the crypto library, the TF-M ported further provides APIs for key generation.

# 3.4.4.4 Cryptographic KeyStore

The platform provides the application with a way to store *cryptographic keys* such that not even the application can compromise the *authenticity, integrity, confidentiality* of this data. This data can be used for the cryptographic operations *encryption, decryption, signature generation, MAC generation, key derivation, shared secret generation.*

#### Conformance rationale: